Transport and logical layer registers, Capability registers (cars), Transport and logical layer registers –26 – Altera RapidIO II MegaCore Function User Manual

Page 164: Capability registers (cars) –26

6–26

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

The RapidIO II IP core transmits the values in the LP-Serial Lane n Status 4 CSR

on the outgoing CS field for lane n.

Transport and Logical Layer Registers

This section lists the Transport and Logical layer registers.

provides a

memory map of all accessible registers. This address space is accessible to the user

through the Maintenance Avalon-MM slave interface.

Capability Registers (CARs)

provides a memory map of all CARs in the RapidIO II IP core. This address

space is accessible to the user through the Register Access Avalon-MM slave interface.

through

describe the capability registers.

Preset

emphasis

[2]

RW

Transmit emphasis command to the connected transceiver to force initial

or preset values. This field is active only when the CMD field has the value

of 1.

2’b0: Ignore.

2’b1: Set all transmit emphasis settings to their preset values.

1’b0

ACK

[1]

RW

Indicates that a transmit emphasis update command from the RapidIO link

partner is being accepted:

1’b0: Command not accepted.

1’b1: Command accepted.

1’b0

NACK

[0]

RW

Indicates that a transmit emphasis update command from the RapidIO link

partner is being refused:

1’b0: Command not refused.

1’b1: Command refused.

1’b0

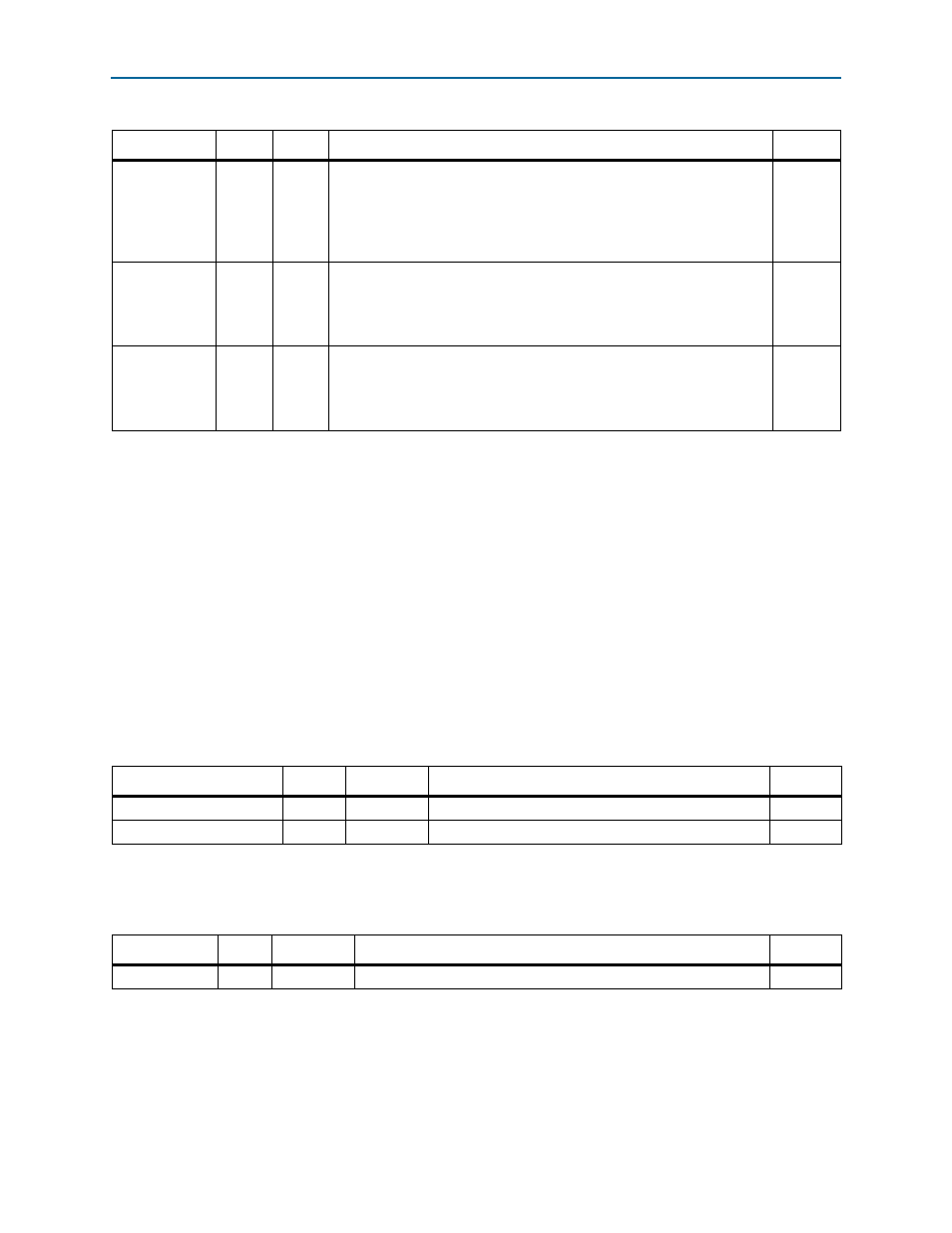

Table 6–21. LP-Serial Lane n Status 4—Outgoing CS Field—Offset: 0x220, 0x240, 0x260, 0x280 (Part 2 of 2)

Field Bits

Access

Function

Default

Table 6–22. Device Identity CAR—Offset: 0x00

Field

Bits

Access

Function

Default

DeviceIdentity

[31:16]

RO

Hard-wired device identifier

DeviceVendorIdentity

[15:0]

RO

Hard-wired device vendor identifier

Note to

:

(1) The value is set in the RapidIO II parameter editor.

Table 6–23. Device Information CAR—Offset: 0x04

Field

Bits

Access

Function

Default

DeviceRev

[31:0]

RO

Hard-wired device revision level

Note to

:

(1) The value is set in the RapidIO II parameter editor.