Altera RapidIO II MegaCore Function User Manual

Page 198

7–4

Chapter 7: Testbench

Testbench Sequence

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

Next, basic programming of the internal registers is performed in the DUT and the

sister_rio module.

shows the registers that are programmed in both the

DUT and the sister_rio IP cores. For a full description of each register, refer to

.

Read and write tasks that are defined in the BFM instance sys_mnt_master_bfm

program the DUT’s registers. Read and write tasks defined in the BFM instance

sister_sys_mnt_master_bfm program the sister_rio module’s registers. For the exact

parameters passed to these tasks, refer to the file tb_rio.v. The tasks drive read and

write transactions across the Register Access Avalon-MM slave interface.

In the configuration shown in

, the IP cores can exchange basic

packets across the serial link.

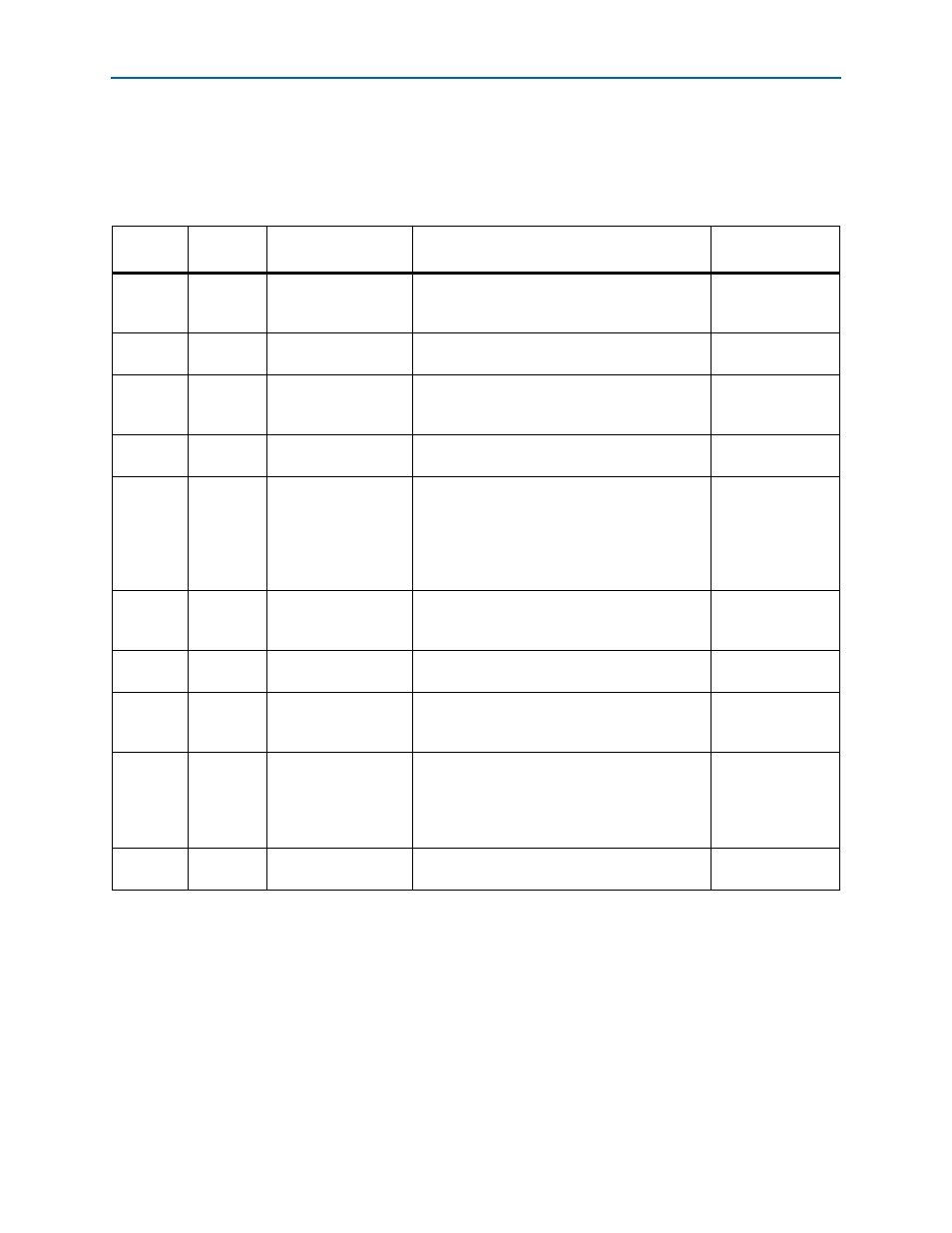

Table 7–1. Testbench Registers

Module

Register

Address

Register Name

Description

Value

rio

0x00060

Base

Device ID CSR

Program the DUT to have an 8-bit base device ID

of 0xAB or a 16-bit device ID of 0xABAB.

32'h00AB_FFFF

or

32’h00FF_ABAB

rio

0x0013C

General

Control

CSR

Enable Request packet generation by the DUT.

32'h6000_0000

sister_rio

0x00060

Base

Device ID CSR

Program the sister_rio module to have an 8-bit

base device ID of 0xCD or a 16-bit device ID of

0xCDCD

.

32'h00CD_FFFF

or

32’h00FF_CDCD

sister_rio

0x0013C

General

Control

CSR

Enable Request packet generation by the

sister_rio module.

32'h6000_0000

rio

0x1040C

Input/Output

Slave

Window

0 Control

Set the DESTINATION_ID for outgoing

transactions to a value 0xCD or 0xCDCD. The

width of the DESTINATION_ID field depends on

the sister_rio device ID width. This value

matches the base device ID of the sister_rio

module.

32'h00CD_0000

or

32'hCDCD_0000

rio

0x10404

Input/Output

Slave

Window

0 Mask

Define the Input/Output Avalon-MM Slave

Window

0 to cover the whole address space

(mask set to all zeros) and enable it.

32'h0000_0004

rio

0x10504

Input/Output

Slave

Interrupt Enable

Enable the I/O slave interrupts.

32'h0000_000F

sister_rio

0x10304

Input/Output

Master

Window 0

Mask

Enable the sister_rio I/O Master Window 0,

which allows the sister_rio to receive I/O

transactions.

32'h0000_0004

rio

0x1010C

TX Maintenance

Window

0 Control

Set the DESTINATION_ID for outgoing

MAINTENANCE

packets to 0xCD or 0xCDCD,

depending on the sister_rio device ID width. This

value matches the base device ID of the sister_rio

module. Set the hop count to 0xFF.

32'h00CD_FF00

or 32'hCDCD_FF00

rio

0x10104

TX

Maintenance

Window

0 Mask

Enable the TX Maintenance window 0.

32'h0000_0004