8 dsp system backgroud debug interface, Figure 5-4, Debug support – Artesyn ATCA-8330 Installation and Use (April 2015) User Manual

Page 112: Functional description

Functional Description

ATCA-8330 Installation and Use (6806800S82B)

112

If the DSP is accessed via SPI-Interface from Glue-Logic FPGA, the address selection has to be

made by SW.

The Artesyn adapter cable #30NL9302D24 is used to connect the 14 pin 100 mil female SBDI

POD to the 16 pin 50 mil male header on the mezzanine card.

5.4.8

DSP System Backgroud Debug Interface

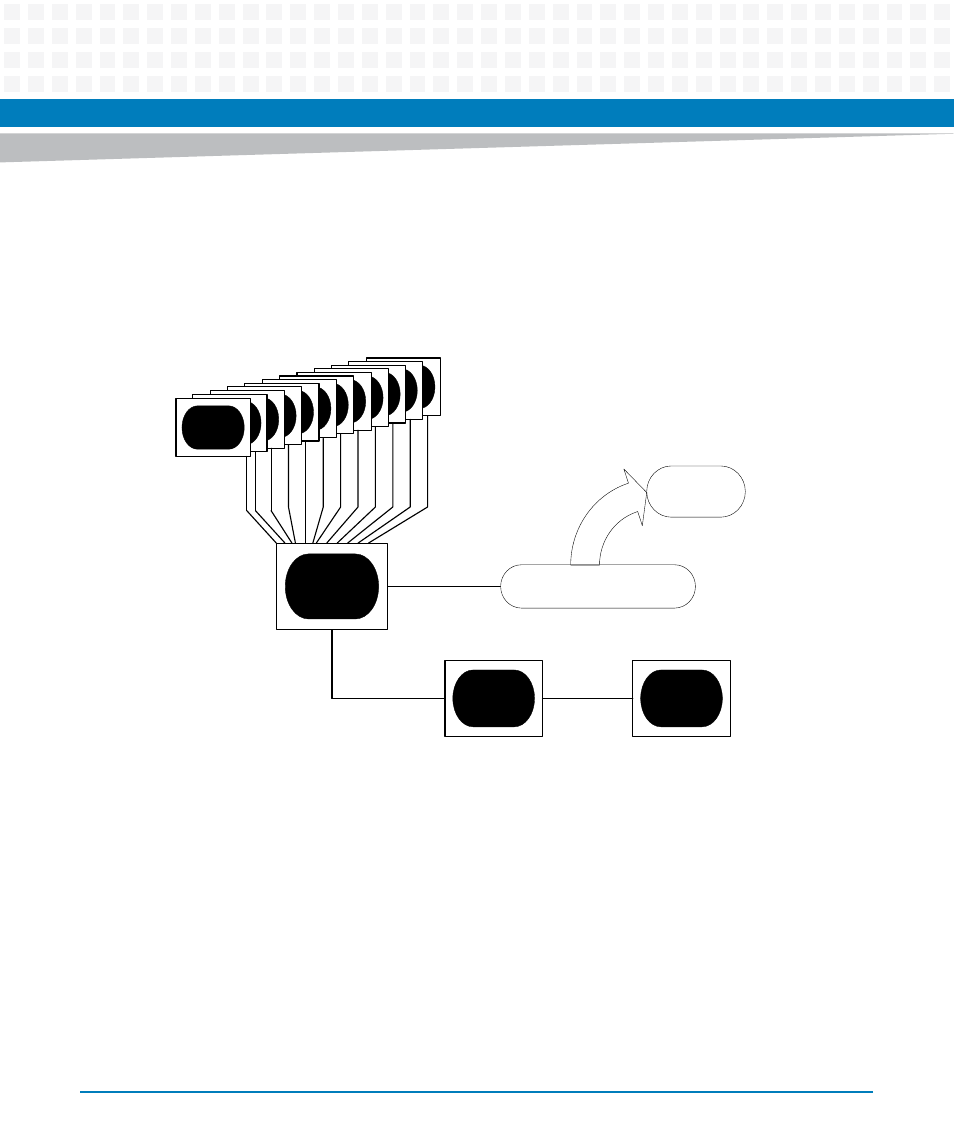

To access the target device, its System Background Debug Interface (SBDI) is connected to a

multiplexer logic at the module. It is selectable via software if the target SBDI is connected to

a debug connector at the module or if this interface is connected via DSP-FPGA to the SPI

interface of the mezzanine connector.

The Debug Connector can be connected to the Octasic System Background Debug Interface

adapter (OCT-SBDI2) via cable.

Figure 5-4

Debug Support

SBDI POD Header

40*SBDI

Cable

OCT

SBDI2

Local Bus

DSP

DSP- FPGA

Glue

DSP-

FPGA

CPU