Chapter 3, Board layout – Lanner LEC-2280 User Manual

Page 19

19

Board Layout

Chapter 3

Embedded and Industrial Computing

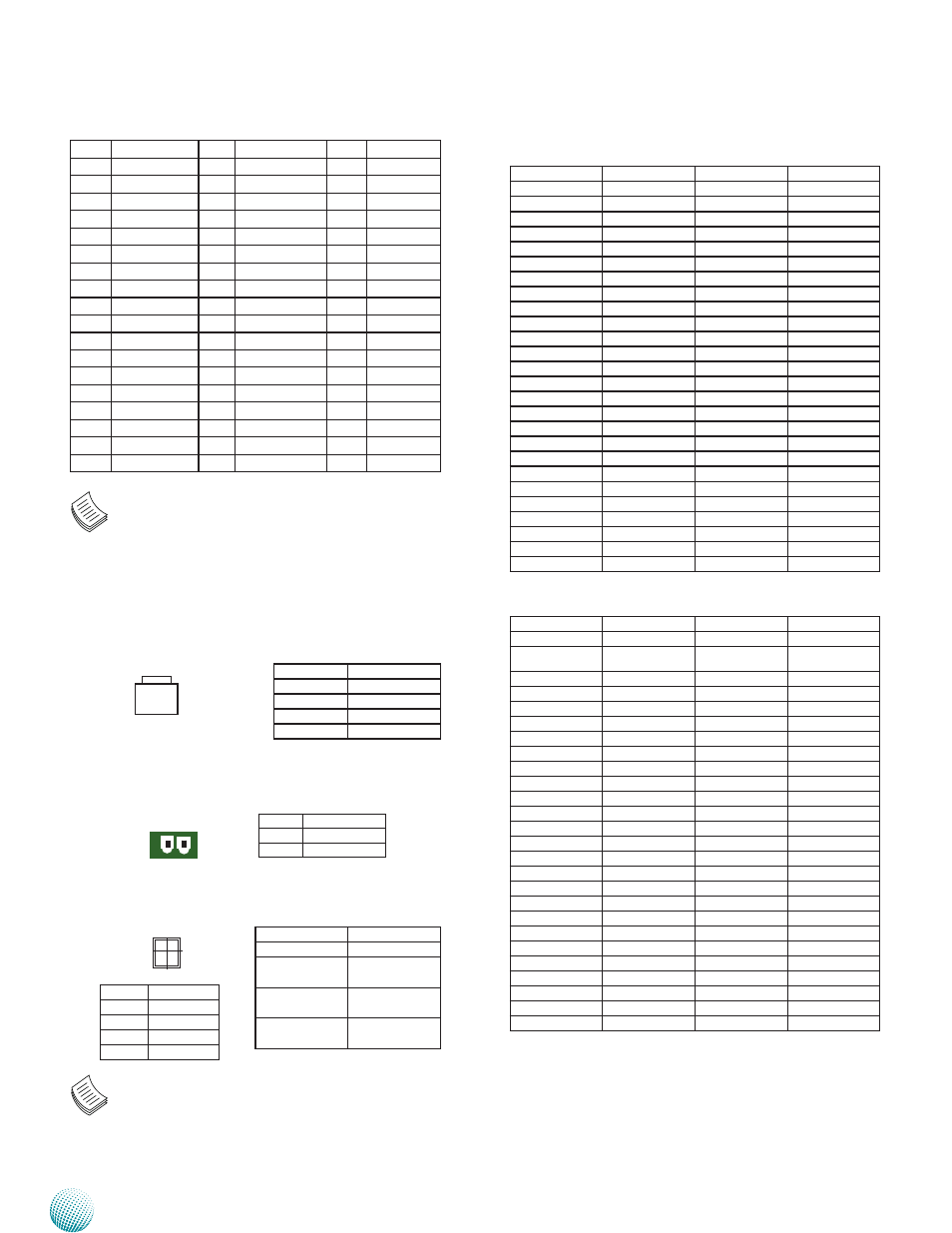

MPCIE1: Mini-PCIe Connector with SIM Card Reader

Pin

signal

Pin

signal

1

WAKE#

2

VCC3.3

3

N/A

4

GNd

5

N/A

6

VCC1.5

7

CLKREQ#

8

UsIM_PWR

9

GNd

10

UIM_dATA

11

PCIE_CLK_N3

12

UIM_CLK

13

PCIE_CLK _P3

14

UIM_REsET

15

GNd

16

UIM_VPP

17

RsV

18

GNd

19

RsV

20

N/A

21

GNd

22

PLTRsT

23

PCIE_RX_N3

24

VCC3.3

25

PCIE_RX_P3

26

GNd

27

GNd

28

VCC1.5

29

GNd

30

sMBCLK

31

PCIE_TX_N3

32

sMBdATA

33

PCIE_TX_P3

34

GNd

35

GNd

36

UsB_N8

37

GNd

38

UsB_P8

39

VCC3.3

40

GNd

41

VCC3.3

42

N/A

43

GNd

44

N/A

45

RsV

46

N/A

47

RsV

48

VCC1.5

49

RsV

50

GNd

51

RsV

52

VCC3.3

MPCIE2: Mini-PCIe Connector

Pin

signal

Pin

signal

1

WAKE#

2

VCC3.3

3

N/A

4

GNd

5

N/A

6

VCC1.5

7

CLKREQ#

8

N/A

9

GNd

10

N/A

11

PCIE_CLK _N4

12

N/A

13

PCIE_CLK _P4

14

N/A

15

GNd

16

N/A

17

RsV

18

GNd

19

RsV

20

N/A

21

GNd

22

PLTRsT

23

PCIE_RX_N4

24

VCC3.3

25

PCIE_RX_P4

26

GNd

27

GNd

28

VCC1.5

29

GNd

30

sMBCLK

31

PCIE_TX_N4

32

sMBdATA

33

PCIE_TX_P4

34

GNd

35

GNd

36

UsB_N9

37

GNd

38

UsB_P9

39

VCC3.3

40

GNd

41

VCC3.3

42

N/A

43

GNd

44

N/A

45

RsV

46

N/A

47

RsV

48

VCC1.5

49

RsV

50

GNd

51

RsV

52

VCC3.3

PIN

SIGNAL

PIN

SIGNAL

PIN

SIGNAL

39

GND

91 PEG_RXN11 143

GND

40

GND

92 PEG_TXN11 144

GND

41

PCIE_RXN2 93 PEG_RXP11 145 PEG_RXN2

42

PCIE_CKN2 94

PEG_TXP11 146 PEG_TXN2

43

PCIE_RXP2

95

GND

147 PEG_RXP2

44

PCIE_CKP2

96

GND

148 PEG_TXP2

45

GND

97 PEG_RXN10 149

GND

46

GND

98 PEG_TXN10 150

GND

47

PCIE_RXP1

99 PEG_RXP10 151 PEG_RXN1

48

PCIE_TXN2 100 PEG_TXP10 152 PEG_TXN1

49

PCIE_RXN1 101

GND

153 PEG_RXP1

50

PCIE_TXP2 102

GND

154 PEG_TXP1

51

GND

103 PEG_RXN9

155

GND

52

GND

104 PEG_TXN9

156

GND

157 PEG_RXN0

158 PEG_TXN0

159 PEG_RXP0

160 PEG_TXP0

Note: Daughter boards such as COM ports and

low-profile PCIe extension boards can only be

inserted to the mainboards with the same version.

Failure to do so may damage the system. The

board version is shown on top of the boards.

Reset Button (RST1)

Pin NO.

description

1

RsT_BTN

2

GNd

3

GNd

4

N/A

DC_IN CONNECTOR (CN4): A Phoenix connector for

external power supply.

J1(PEG 16X lane Configuration): PCI/PCIe (PCIEIO1)

expansion connector signal selection

Pin

Lane

All Off

x16

1-2 ON

3-4 Off (default)

x8, x8

1-2 OFF

3-4 ON

Reserved

1-2 ON

3-4 ON

x8, x4, x4

Note: For PEG riser card, PEG lanes is reversed for

layout limited

Pin No.

Pin Name

1

GNd

2

dC_VIN

1

3

2

4

1 2

1

3

2

4

Pin No.

signal

1

GNd

2

H_CFG5

3

GNd

4

H_CFG6