Figure 4–3 – Altera Nios II C2H Compiler User Manual

Page 103

Altera Corporation

9.1

4–9

November 2009

Nios II C2H Compiler User Guide

Understanding the C2H View

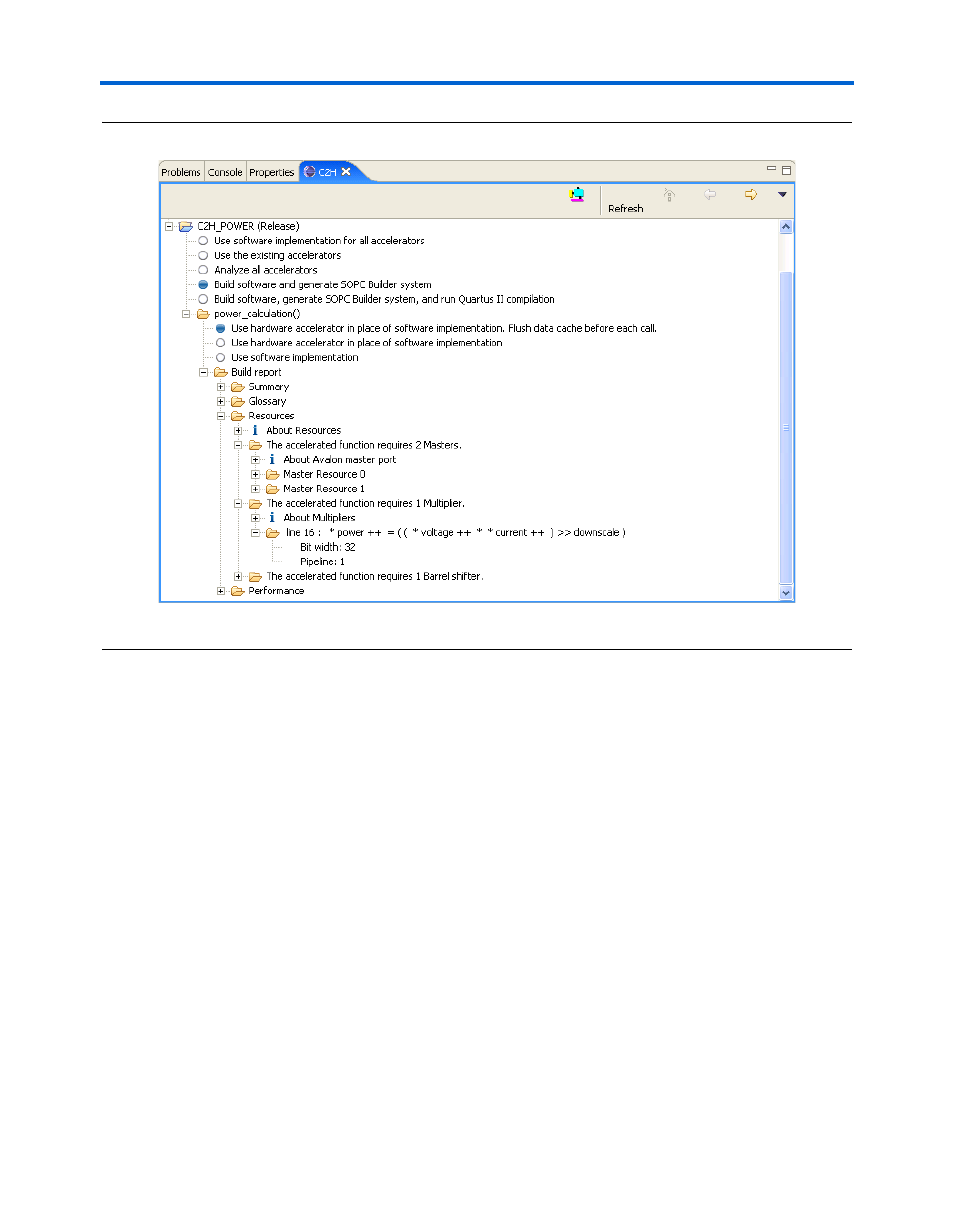

Figure 4–3. Multiplier Resources

1

The resource usage does not reflect the final resource utilization

of the compiled hardware. When ANSI C code is compiled,

small integer data types are promoted to the

int

data type. In

we can see that the multiplier is 32 bits wide even

though the operands are

short

(16 bits). The C2H Compiler

performs the same integer data promotion, creating a 32-bit

multiplier. When the Quartus II software compiles the hardware

design, the synthesized multiplier is 16 bits in width.

The pipeline value associated with the resource specifies the number of

clock cycles that the hardware logic requires for the calculation to

complete. Pipelined logic can typically operate at higher clock

frequencies due to the additional latency introduced. The C2H Compiler

factors in the pipelining of the hardware and schedules the accelerated

function accordingly to maximize data throughput. When the report does

not show a pipeline value for a resource, that means that the operator is

purely combinational, with no latency.