Address computation – Altera Nios II C2H Compiler User Manual

Page 61

Altera Corporation

9.1

3–21

November 2009

Nios II C2H Compiler User Guide

C-to-Hardware Mapping Reference

Each of these signals is registered at the master port interface of the

hardware accelerator. Logic within the accelerator synchronizes these

signals to produce coherent Avalon-MM master transfers at the master

port.

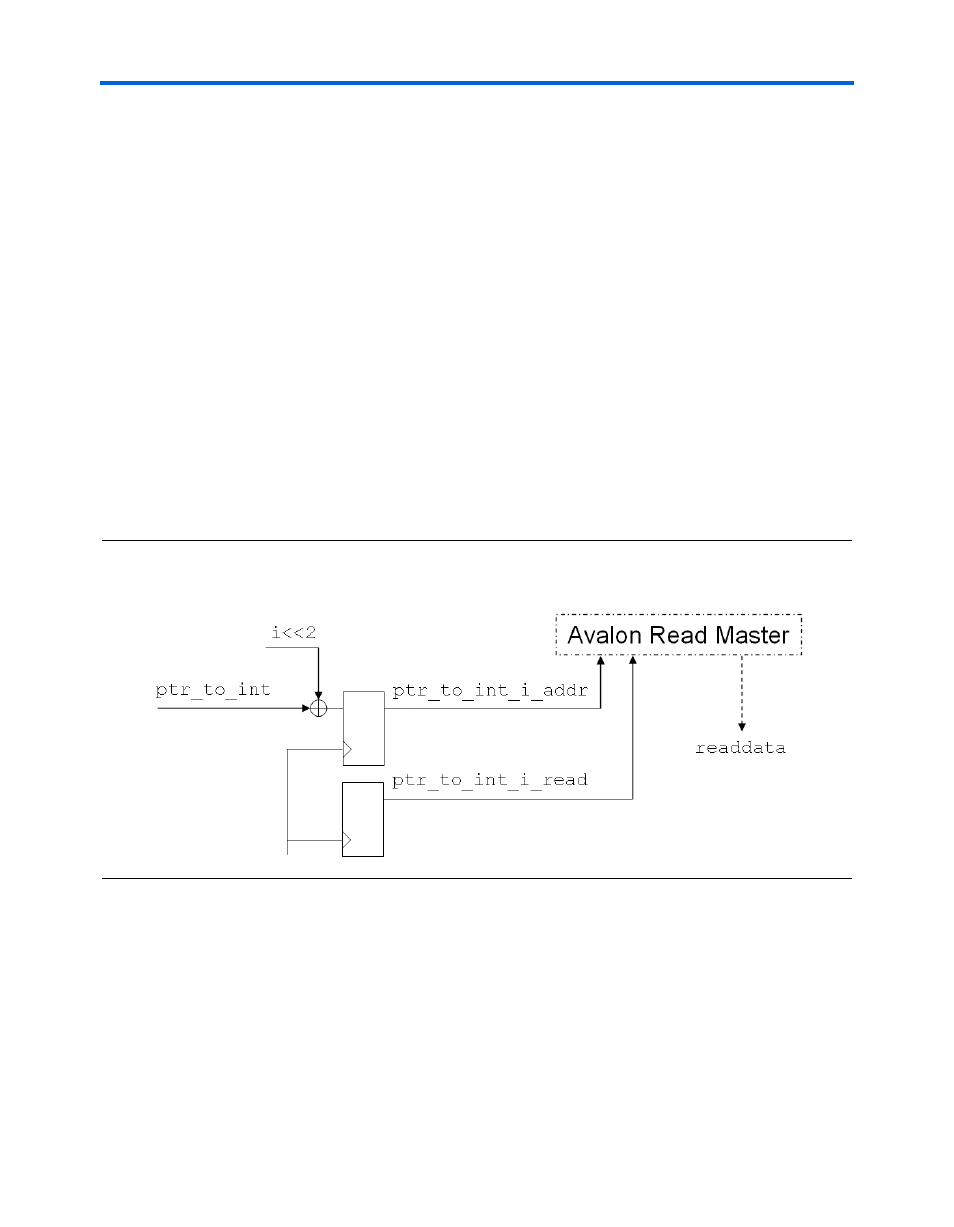

Address Computation

Consider the pointer dereference in the following code which performs a

read operation:

int j = *(ptr_to_int + i);

The C2H Compiler generates logic of the following form to compute the

address signal:

ptr_to_int_i_addr = ptr_to_int + i * sizeof(int);

shows an example of the logic created for this pointer

dereference for a read operation.

Figure 3–9. Address Generation for a Read Operation

In

, first, the address expression is evaluated. Assuming

sizeof(int)

is 4,

i

must be multiplied by four, which is equivalent to

left-shifting by 2 bits. Bitwise shift operators require no logic elements to

compute, and the result is not registered. (See section

Operations and Assignments” on page 3–3

.) The signal

ptr_to_int_i_address

feeds registers that drive the address signals

on the Avalon-MM master port. As soon as the address signal

ptr_to_int_i_address

is valid, read-enable control logic asserts the

signal

ptr_to_int_i_read

, which initiates a transfer on the master