Vhdl library-use declaration – Altera RAM-Based Shift Register User Manual

Page 22

3–2

Chapter 3: Specifications

VHDL Library-Use Declaration

RAM-Based Shift Register (ALTSHIFT_TAPS) Megafunction User Guide

May 2013

Altera Corporation

VHDL Library-Use Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL

component declaration.

LIBRARY alterea_mf;

USE altera_mf.altera_mf_components.all;

Ports and Parameters for the ALTSHIFT_TAPS Megafunction

below shows the ports and parameters for the ALTSHIFT_TAPS

megafunction.

The parameter details are only relevant for users who bypass the MegaWizard

®

Plug-In Manager interface and use the megafunction as a directly parameterized

instantiation in their design. The details of these parameters are hidden from

MegaWizard Plug-In Manager interface users.

shows the input ports of the ALTSHIFT_TAPS megafunction.

shows the output ports of the ALTSHIFT_TAPS megafunction.

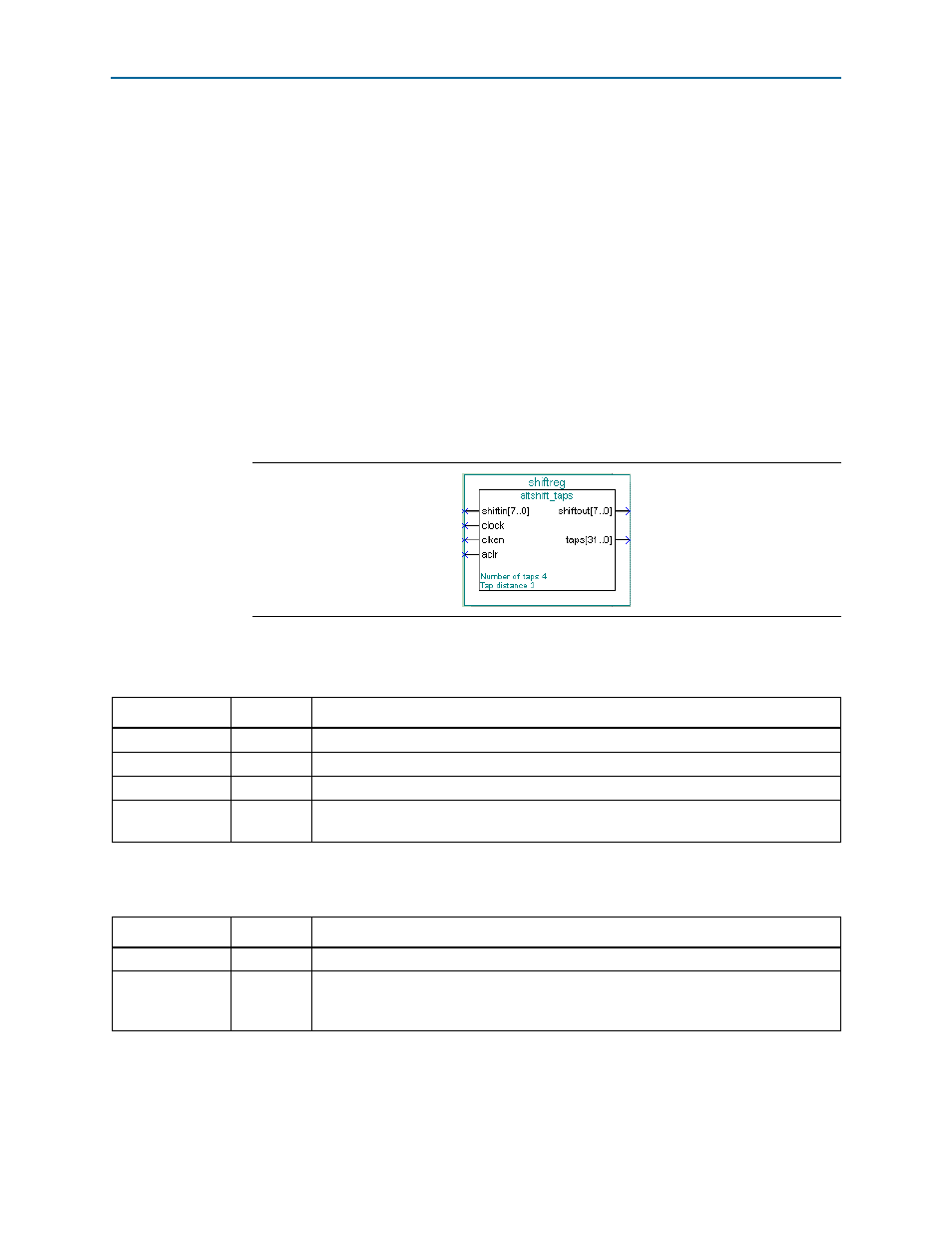

Figure 3–1. Shift Register (RAM-based) Ports and Parameters

Table 3–1. Shift Register (RAM-based) MegaWizard Plug-In Manager Input Ports

Name

Required

Description

shiftin[]

Yes

Data input to the shifter. Input port WIDTH bits wide.

clock

Yes

Positive-edge triggered clock.

clken

No

Clock enable for the clock port. clken defaults to V

CC

.

aclr

No

Asynchronously clears the contents of the shift register chain. The shiftout outputs are

cleared immediately upon the assertion of the aclr signal.

Table 3–2. Shift Register (RAM-based) MegaWizard Plug-In Manager Output Ports

Name

Required

Description

shiftout[]

Yes

Output from the end of the shift register. Output port WIDTH bits wide.

taps[]

Yes

Output from the regularly spaced taps along the shift register. Output port WIDTH *

NUMBER_OF_TAPS

wide. This port is an aggregate of all the regularly spaced taps (each

WIDTH

bits) along the shift register.