Altera RAM-Based Shift Register User Manual

Page 9

Chapter 2: Getting Started

2–3

MegaWizard Plug-In Manager Page Descriptions

May 2013

Altera Corporation

RAM-Based Shift Register (ALTSHIFT_TAPS) Megafunction User Guide

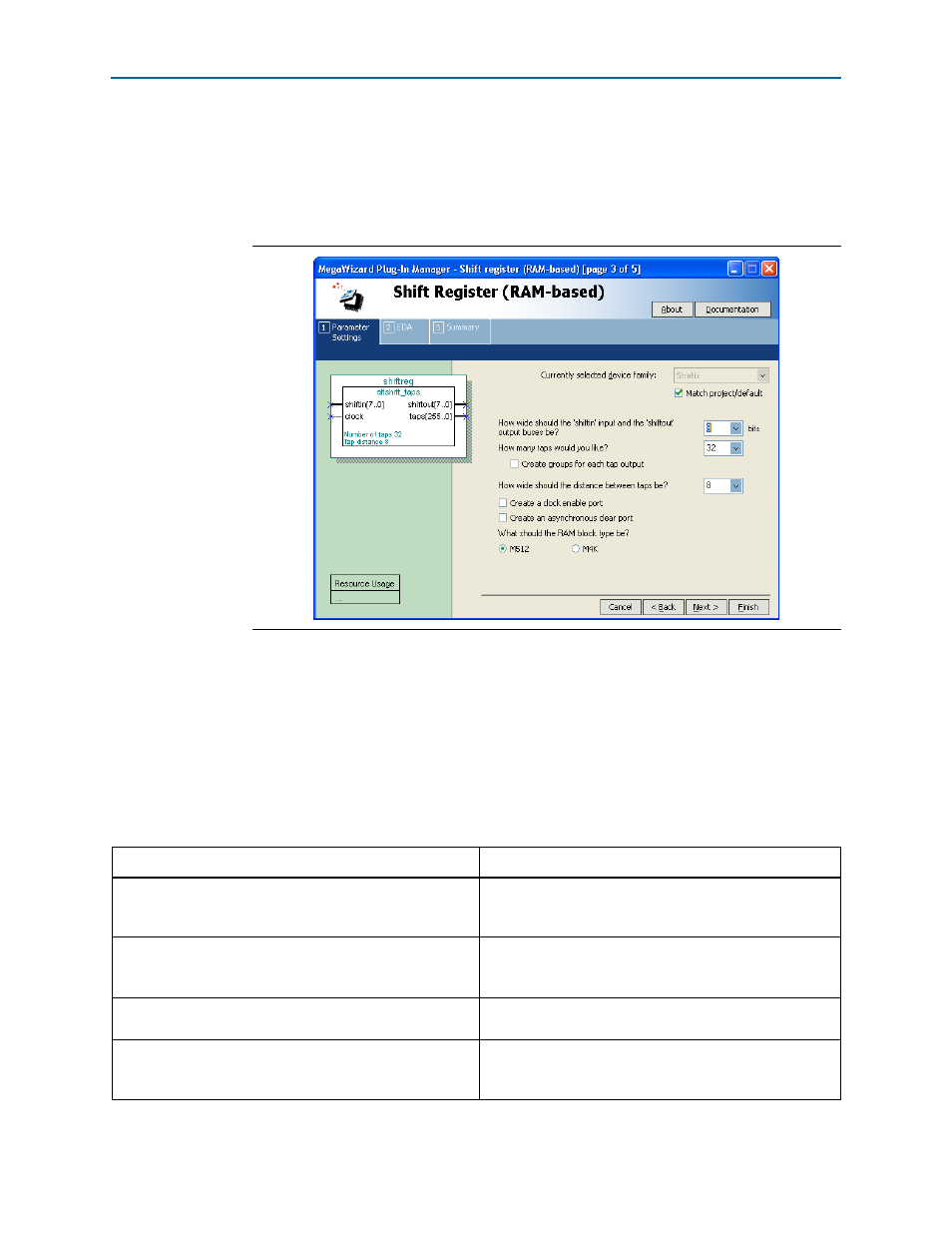

On page 3 of the MegaWizard Plug-In Manager, specify the width of the shiftin

input bus and the shiftout output bus, specify the number of taps, create groups for

each tap output, and specify the distance between the taps. You can also create a

clock-enable port and an asynchronous-clear port, if applicable to your design, and

select the type of RAM block type to use (

1

Starting on page 3 of the Shift Register (RAM-based) MegaWizard Plug-In Manager,

you can launch the Shift Register (RAM-based) (ALTSHIFT_TAPS) Megafunction User

Guide, the ALTSHIFT_TAPS megafunction online help, or generate sample waveforms

by clicking the Documentation button.

shows the options available on page 3 of the Shift Register (RAM-based)

MegaWizard Plug-In Manager. Use this table, along with the hardware descriptions,

to determine the appropriate settings for the features.

Figure 2–3. MegaWizard Plug-In Manager – Shift Register (RAM-based) [page 3 of 5]

Table 2–1. Shift Register (RAM-based) MegaWizard Plug-in Manager [page 3] Options (Part 1 of 2)

Configuration Setting

Description

How wide should the ‘shiftin’ input and the ‘shiftout’

output buses be?

Specify the width of the data input and output buses. This

value is represented by the term w in the Shift Register

Memory Configuration shown in

How many taps would you like?

Specify the number of taps. This value is represented by the

term n in the Shift Register Memory Configuration shown in

.

Create groups for each tap output

Turn on this option to create separate groups for output data

tapped from the register chain.

How wide should the distance between taps be?

Specify the distance between taps. This value is represented

by the term m in the Shift Register Memory Configuration

shown in