Altera Phase-Locked Loop User Manual

Page 11

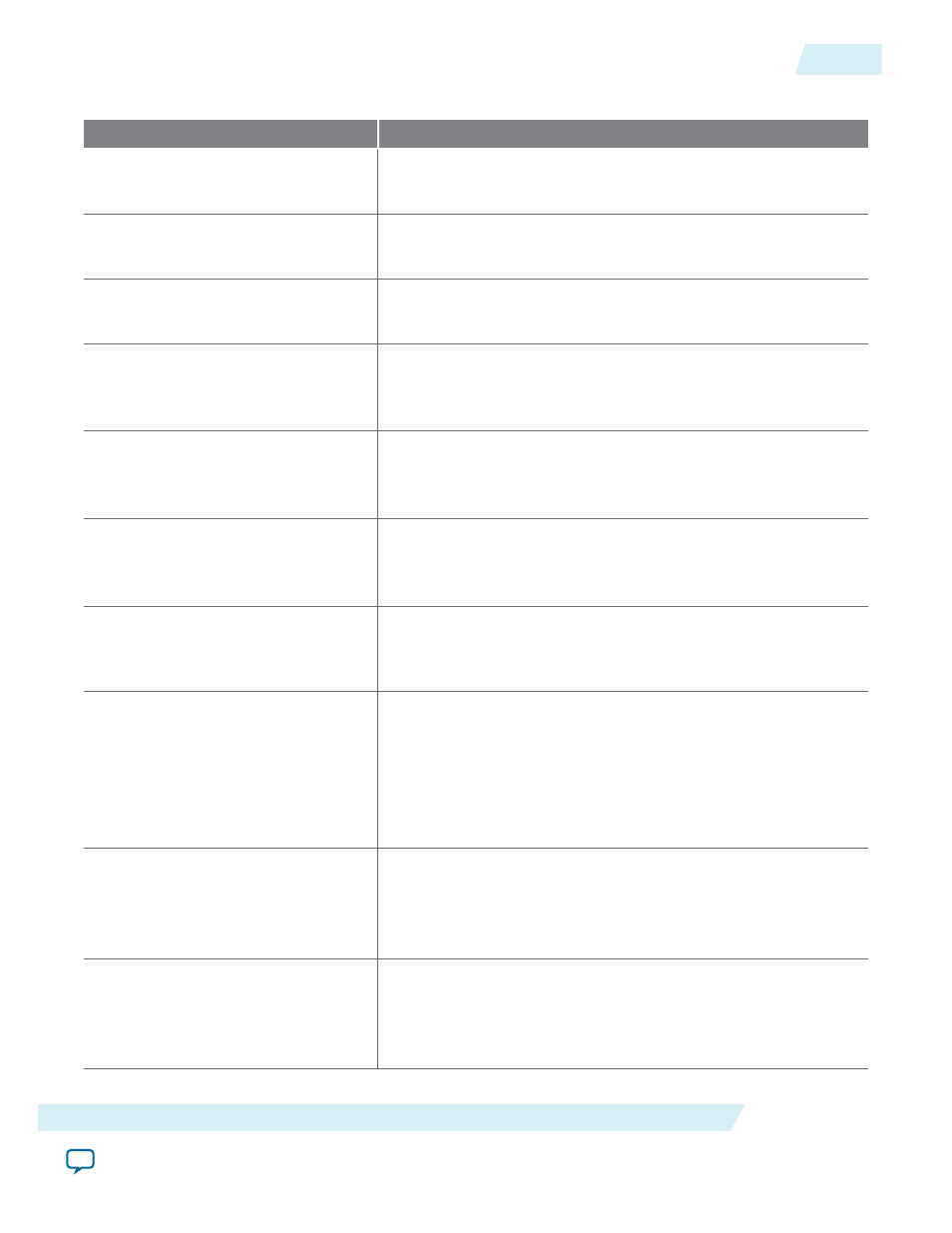

Table 7:

adjpllin

Cascading for Supported Devices

Device

adjpllin Cascading (Upstream PLL — Downstream PLL)

• Arria V GX B5 and B7

• Arria V GT D7

•

FRACTIONALPLL_X0_Y96

—

FRACTIONALPLL_X0_Y63

•

FRACTIONALPLL_X183_Y96

—

FRACTIONALPLL_X183_Y63

Arria V GZ E5 and E7

•

FRACTIONAL_X0_Y31

—

FRACTIONALPLL_X0_Y46

•

FRACTIONALPLL_X202_Y31

—

FRACTIONALPLL_X202_Y46

• Arria V SX B3 and B5

• Arria V ST D3 and D5

FRACTIONALPLL_X0_Y96

—

FRACTIONALPLL_X0_Y63

• Cyclone V E A5

• Cyclone V GX C4 and C5

• Cyclone V GT D5

FRACTIONALPLL_X0_Y14

—

FRACTIONALPLL_X0_Y30

• Cyclone V E A7

• Cyclone V GX C7

• Cyclone V GT D7

FRACTIONALPLL_X0_Y15

—

FRACTIONALPLL_X0_Y32

• Cyclone V E A9

• Cyclone V GX C9

• Cyclone V GT C9

•

FRACTIONALPLL_X0_Y22

—

FRACTIONALPLL_X0_Y39

•

FRACTIONALPLL_X0_Y64

—

FRACTIONALPLL_X0_Y81

• Stratix V GS D5

• Stratix V GX A3 (with 36

transceivers) and A4

•

FRACTIONALPLL_X0_Y31

—

FRACTIONALPLL_X0_Y46

•

FRACTIONALPLL_X202_Y31

—

FRACTIONALPLL_X202_Y46

Stratix V GX B5 and B6

•

FRACTIONALPLL_X0_Y14

—

FRACTIONALPLL_X0_Y30

•

FRACTIONALPLL_X0_Y76

—

FRACTIONALPLL_X0_Y63

•

FRACTIONALPLL_X0_Y100

—

FRACTIONALPLL_X0_Y85

•

FRACTIONALPLL_X197_Y14

—

FRACTIONALPLL_X197_Y30

•

FRACTIONALPLL_X197_Y76

—

FRACTIONALPLL_X197_Y63

•

FRACTIONALPLL_X197_Y100

—

FRACTIONALPLL_X197_Y85

• Stratix V GT C5 and C7

• Stratix V GX A5 and A7

•

FRACTIONALPLL_X0_Y29

—

FRACTIONALPLL_X0_Y44

•

FRACTIONALPLL_X0_Y91

—

FRACTIONALPLL_X0_Y75

•

FRACTIONALPLL_X210_Y29

—

FRACTIONALPLL_X210_Y44

•

FRACTIONALPLL_X210_Y91

—

FRACTIONALPLL_X210_Y75

Stratix V GS D6 and D8 Devices

•

FRACTIONALPLL_X0_Y41

—

FRACTIONALPLL_X0_56

•

FRACTIONALPLL_X0_Y103

—

FRACTIONALPLL_X0_Y87

•

FRACTIONALPLL_X208_Y41

—

FRACTIONALPLL_X208_56

•

FRACTIONALPLL_X208_Y103

—

FRACTIONALPLL_X208_Y87

UG-01087

2015.05.04

PLL-to-PLL Cascading

11

Altera Phase-Locked Loop (Altera PLL) IP Core User Guide

Altera Corporation