Document revision history – Altera Phase-Locked Loop User Manual

Page 17

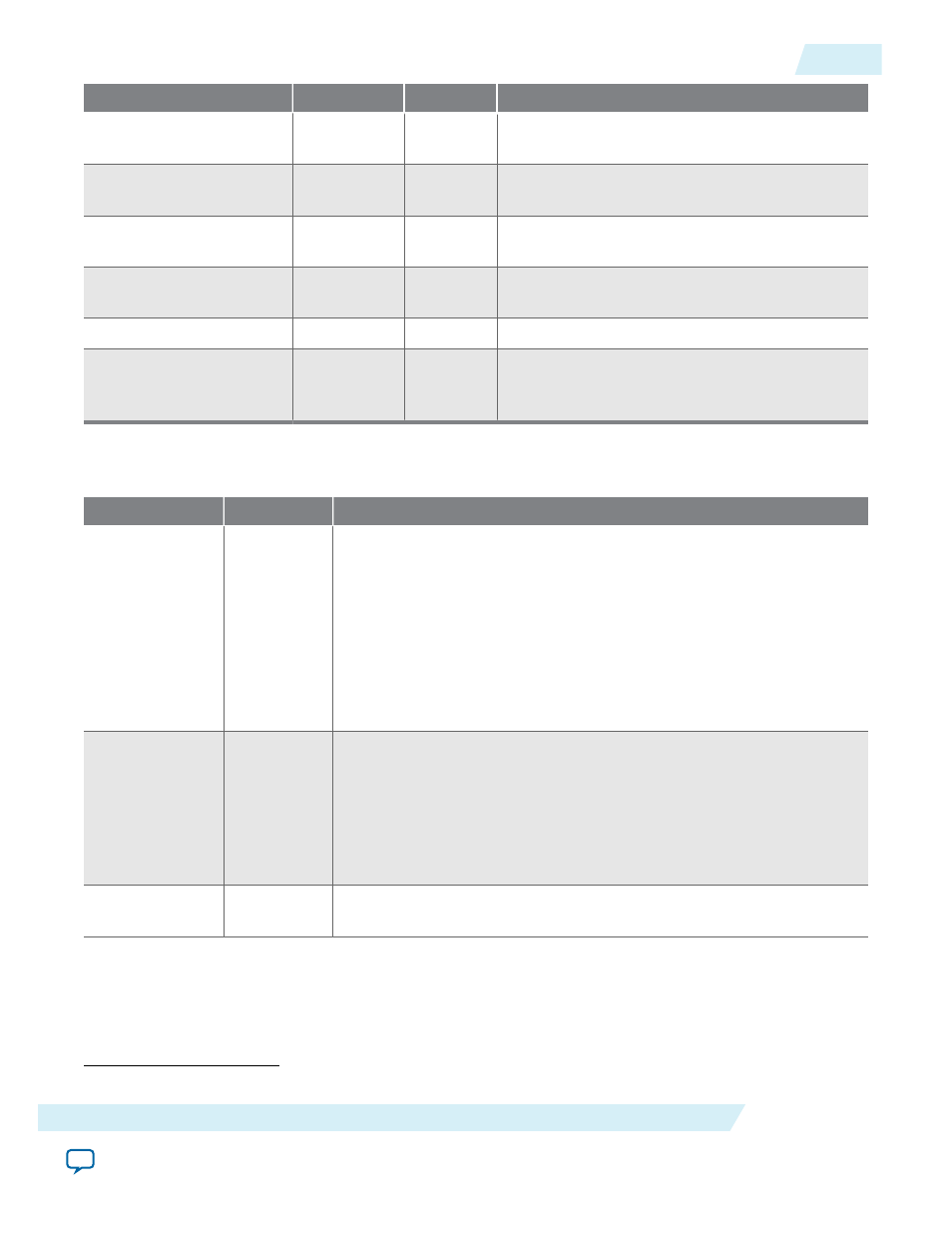

Port Name

Type

Condition

Description

extswitch

Input

Required Assert this input signal high (1’b1) to manually

switch the clock for at least 3 cycles.

activeclk

Output

Optional Output signal to determine which input clock is

in use by the PLL.

clkbad

Output

Optional Output signal to determine which input clock is

working.

cclk

(8)

Input

Optional

C

-Counter clock source from the fracturable

fractional PLL output counter 4 or 13.

adjpllin

Input

Optional Adjacent fractional PLL clock source.

cascade_out

Output

Optional Output signal to feed into other fractional PLLs.

This port acts as a bus port when the upstream

PLL has two or more output clocks.

Document Revision History

Date

Version

Changes

May 2015

2015.05.04 • Added Arria V and Cyclone V devices in

adjpllin

Cascading for

Supported Devices table.

•

cclk

input clock source is not supported in Cyclone V devices.

Updated the information and notes in the following locations:

• Altera PLL IP Core Parameters - Cascading Tab table

• PLL-to-PLL Cascading section

• Reference Clock Inputs for Fractional PLL table

• Altera PLL Ports table

August 2014

2014.08.01 • Grouped parameters in separate tables according to parameter editor

tabs.

• Added parameters for the General tab and Cascading tab.

• Updated parameters for the Clock Switchover tab.

• Updated information on PLL-to-PLL Cascading.

• Added information on PLL output counter cascading.

December

2013

1.3

Updated Table 3 on page 10 to update reset port information.

(8)

Not supported in Cyclone V devices.

UG-01087

2015.05.04

Document Revision History

17

Altera Phase-Locked Loop (Altera PLL) IP Core User Guide

Altera Corporation