Altera pll ip core parameters - settings tab, Functional description – Altera Phase-Locked Loop User Manual

Page 7

Parameter

Legal Value

Description

Number of Dynamic Phase

Shifts

—

Selects the number of phase shift increments. The size of a

single phase shift increment is equal to 1/8 of the VCO

period. The default value is 1.

Dynamic Phase Shift

Direction

Positive or

Negative

Determines the dynamic phase shift direction to store into

the PLL MIF.

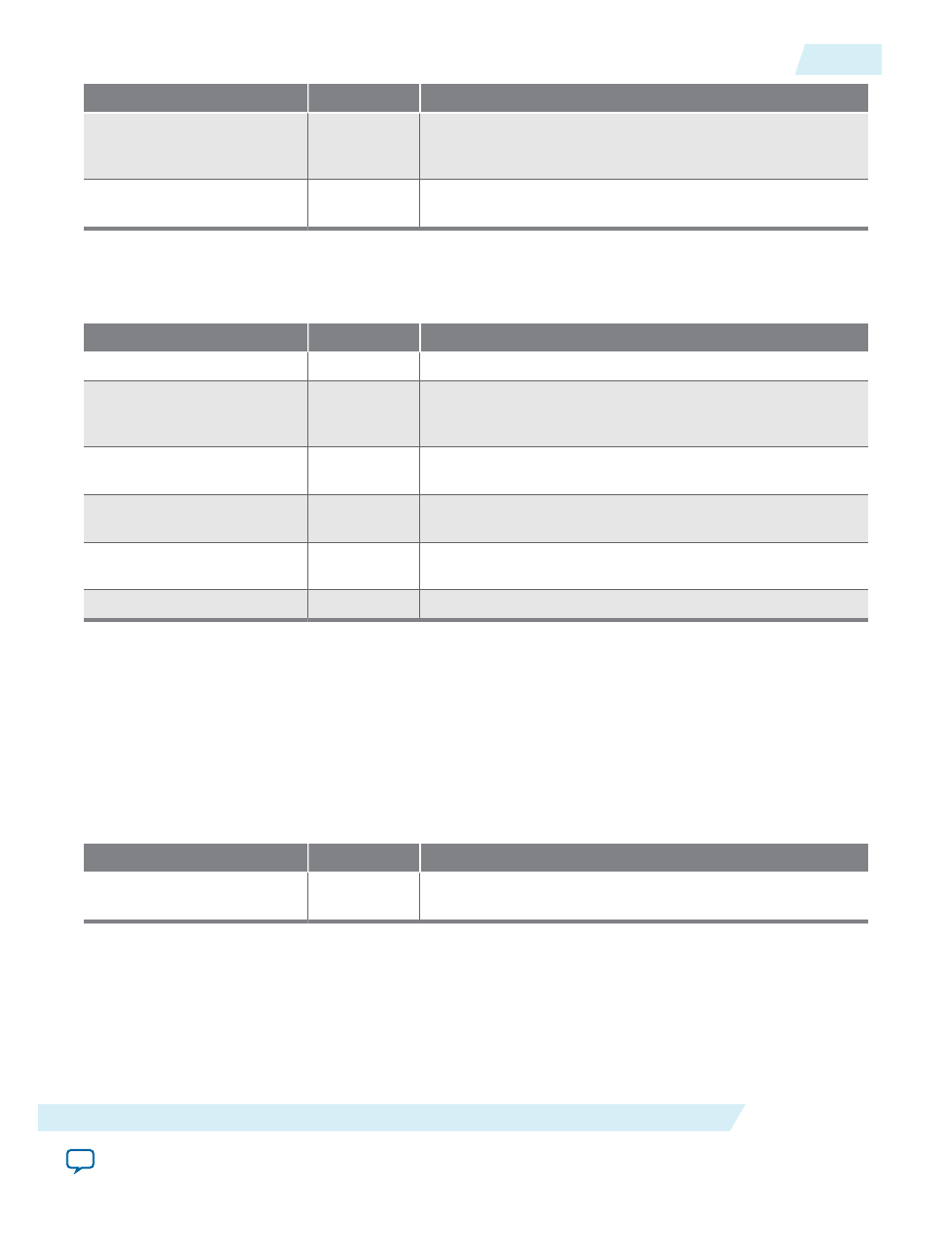

Altera PLL IP Core Parameters - Settings Tab

Table 5: Altera PLL IP Core Parameters - Settings Tab

Parameter

Legal Value

Description

PLL Auto Reset

On or Off

Automatically self-resets the PLL on loss of lock.

PLL Bandwidth Preset

Auto, High,

Low, or

Medium

Specifies the PLL bandwidth preset setting. The default

setting is Auto.

Enable dynamic reconfigu‐

ration of PLL

Turn on or

Turn off

Turn on to enable the dynamic reconfiguration of the PLL.

Enable access to dynamic

phase shift ports

Turn on or

Turn off

Turn on to enable the dynamic phase shift interface with the

PLL.

Enable access to PLL DPA

output port

Turn on or

Turn off

Turn on to enable the eight bits port for the eight phases of

the DPA clock.

PLL DPA output division

1, 2, or 4

Specifies the PLL DPA output division value.

Related Information

•

Provides more information about PLL dynamic reconfiguration and dynamic phase shift.

•

Altera PLL IP Core Parameters - Advanced Parameters Tab

Table 6: Altera PLL IP Core Parameters - Advanced Parameters Tab

Parameter

Legal Value

Description

Advanced Parameters

—

Displays a table of physical PLL settings that will be

implemented based on your input.

Functional Description

A PLL is a frequency-control system that generates an output clock by synchronizing itself to an input

clock. The PLL compares the phase difference between the input signal and the output signal of a voltage-

controlled oscillator (VCO). The PLL performs phase synchronization to maintain a constant phase angle

UG-01087

2015.05.04

Altera PLL IP Core Parameters - Settings Tab

7

Altera Phase-Locked Loop (Altera PLL) IP Core User Guide

Altera Corporation