Pll output counter cascading – Altera Phase-Locked Loop User Manual

Page 14

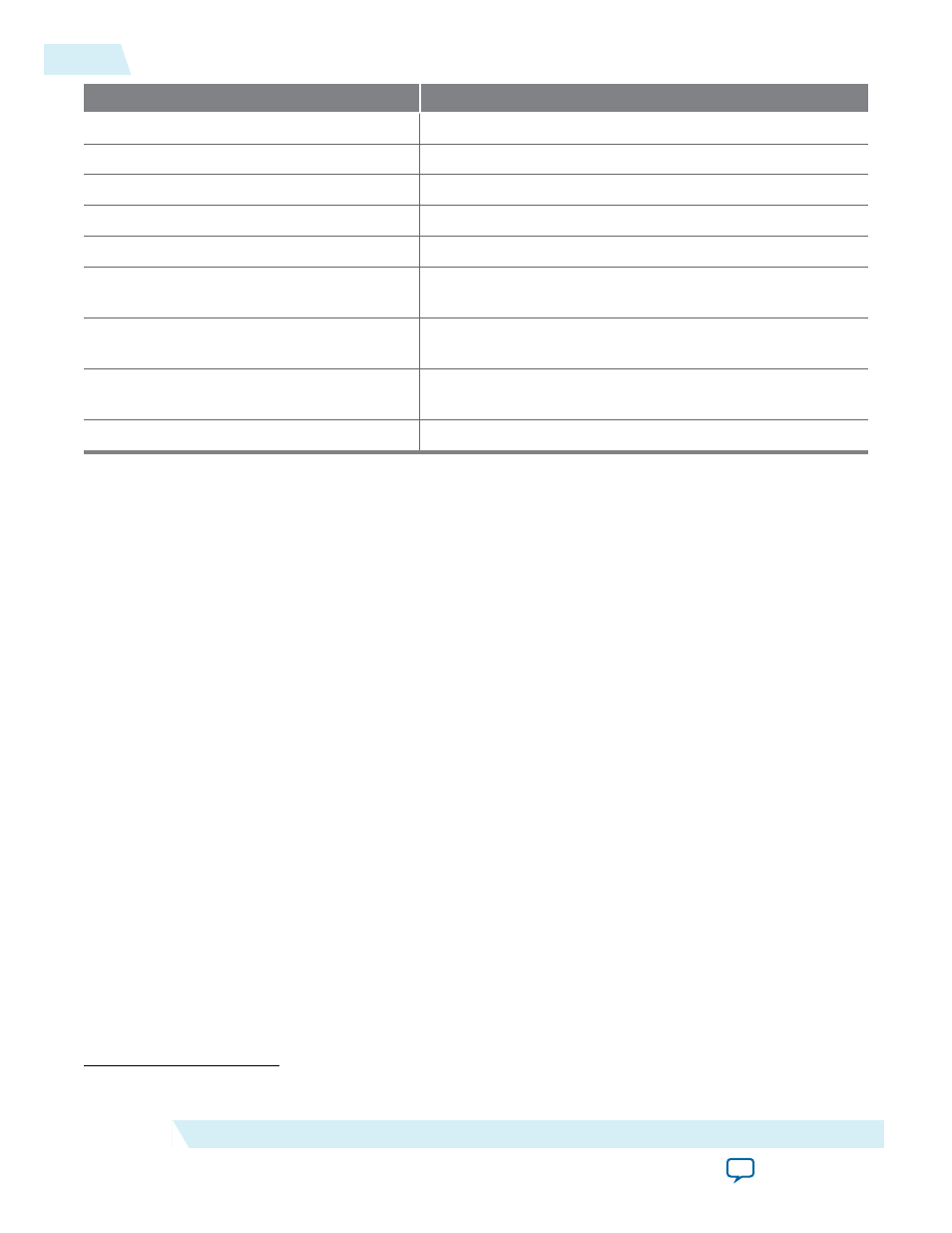

Sources

Description

refclkin[1]

Clock source from adjacent PMA triplet LVPECL buffer.

clkin[0]

Dedicated clock input for fractional PLL from regular I/O.

clkin[1]

Dedicated clock input for fractional PLL from regular I/O.

clkin[2]

Dedicated clock input for fractional PLL from regular I/O.

clkin[3]

Dedicated clock input for fractional PLL from regular I/O.

rxiqclk

Clock source from adjacent PMA triplet

rxiqclknet

. For

refclk

and PMA/LC cascading with fractional PLL.

refiqclk

Clock source from adjacent PMA triplet

rxiqclknet

as

refclk

.

iqtxrxclk

Clock source from adjacent PMA triplet

iqtxrxclk

as

refclk

.

cclk

(7)

C

-Counter clock source.

PLL Output Counter Cascading

The Altera 28 nm devices instantiate the Altera PLL IP core to allow output counter cascading. PLL

cascading enables PLL to synthesize a lower frequency output which is not achievable with a single

counter output.

This feature is only accessible when Enable physical output clock parameters is turned on. Turn on

Make this a cascade counter to select an

outclk

port as the upstream counter. The upstream counter

serves as the reference clock to the downstream counter and not available as a PLL output.

Only the upstream counter in the PLL output counter cascade chain supports phase shifting and only the

downstream counter in the cascade chain support programmable duty cycle.

(7)

Not supported in Cyclone V devices.

14

PLL Output Counter Cascading

UG-01087

2015.05.04

Altera Corporation

Altera Phase-Locked Loop (Altera PLL) IP Core User Guide