Ports – Altera Phase-Locked Loop User Manual

Page 16

Ports

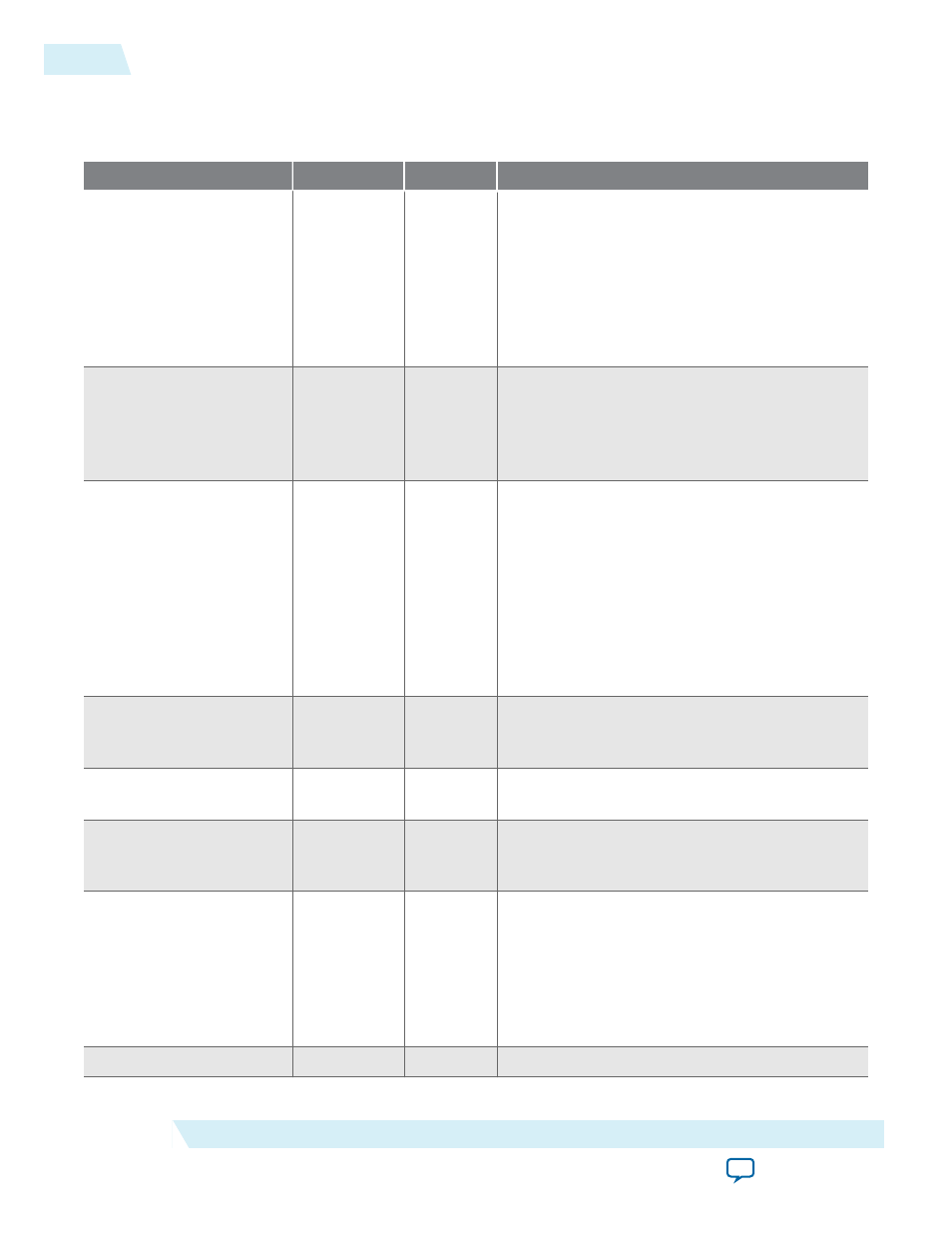

Table 9: Altera PLL Ports

Port Name

Type

Condition

Description

fbclk

Input

Optional The external feedback input port for the PLL.

The Altera PLL IP core creates this port when

the PLL is operating in external feedback mode

or zero-delay buffer mode. To complete the

feedback loop, a board-level connection must

connect the

fbclk

port and the external clock

output port of the PLL.

fboutclk

Output

Optional The port that feeds the

fbclk

port through the

mimic circuitry.

The

fboutclk

port is available only if the PLL is

in external feedback mode.

locked

Output

Optional The Altera PLL IP core drives this port high

when the PLL acquires lock. The port remains

high as long as the PLL is locked.

The PLL asserts the

locked

port when the phases

and frequencies of the reference clock and

feedback clock are the same or within the lock

circuit tolerance. When the difference between

the two clock signals exceeds the lock circuit

tolerance, the PLL loses lock.

outclk[]

Output

Required The clock output of the PLL. The frequency of

the output clock depends on the parameter

settings.

refclk

Input

Required The reference clock that drives the clock

network.

reset

Input

Required The asynchronous reset port for the output

clocks. Drive this port high to reset all output

clocks to the initial value of 0.

zdbfbclk

Bidirectional

Optional The bidirectional port that connects to the

mimic circuitry. This port must connect to a

bidirectional pin that is placed on the positive

feedback dedicated output pin of the PLL.

The

zdbfbclk

port is available only if the PLL is

in zero-delay buffer mode.

refclk1

Input

Required Second input clock signal that feeds into the PLL.

16

Ports

UG-01087

2015.05.04

Altera Corporation

Altera Phase-Locked Loop (Altera PLL) IP Core User Guide