Altera Phase-Locked Loop User Manual

Page 4

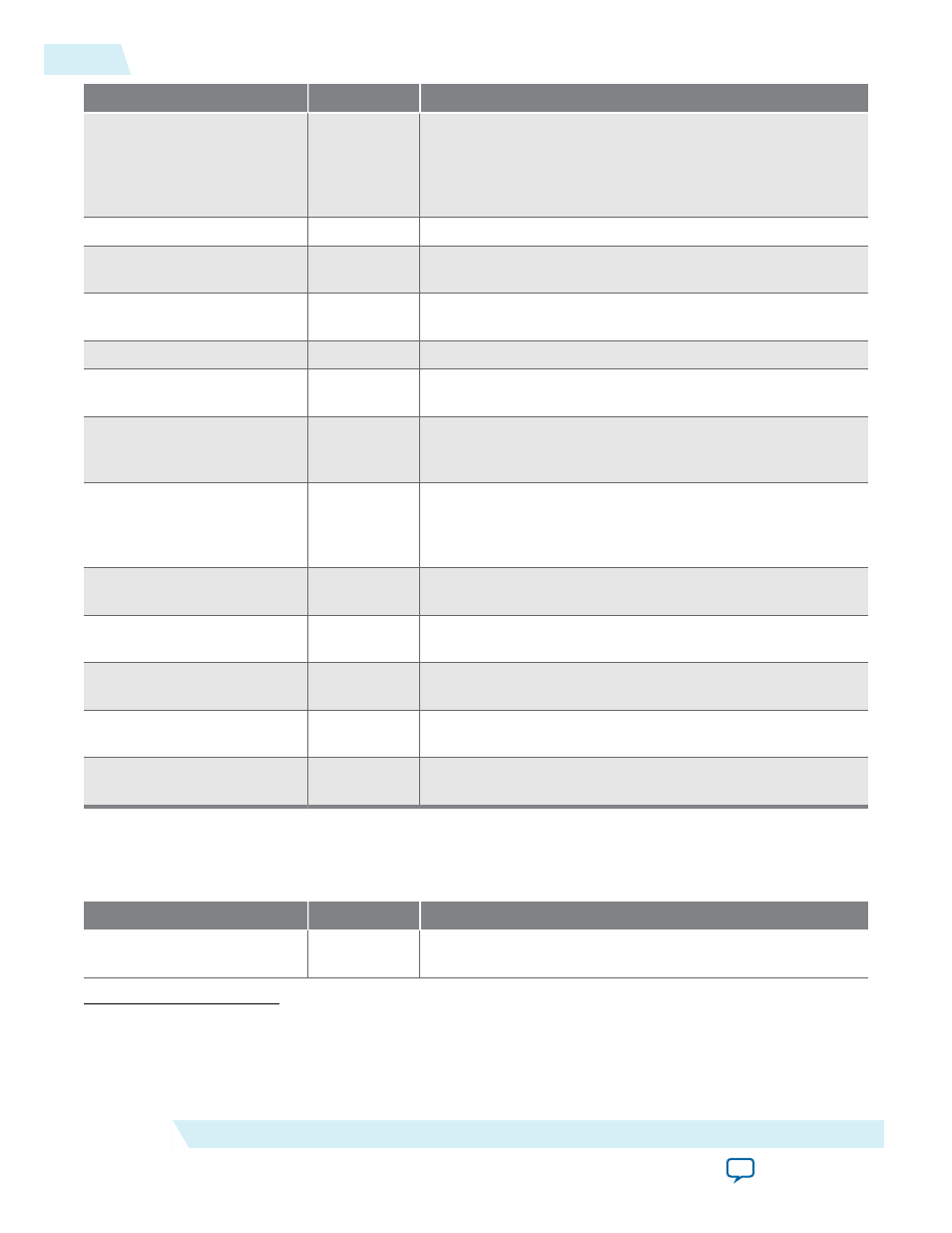

Parameter

Legal Value

Description

Desired Frequency

(1)

—

Specifies the output clock frequency of the corresponding

output clock port,

outclk[]

, in MHz. The default value is

100.0 MHz. The minimum and maximum values depend on

the device used. The PLL only reads the numerals in the first

six decimal places.

Actual Frequency

—

Specifies the actual value for the output clock frequency.

Phase Shift units

ps or degrees Specifies the phase shift unit for the corresponding output

clock port,

outclk[]

, in picoseconds (ps) or degrees.

Phase Shift

—

Specifies the requested value for the phase shift. The default

value is 0 ps.

Actual Phase Shift

—

Specifies the actual value for the phase shift.

Duty Cycle

1–99

Specifies the duty cycle in percentage for the corresponding

output clock port,

outclk[]

. The default value is 50%.

Fractional carry out

(2)(3)

8, 16, 24, or 32 Specifies the fractional carry out (

Fcout

) for the Delta Sigma

Modulator (DSM) mode for PLL. The fractional carry out

determines the denominator in the equation K/2^

Fcout

.

DSM Order

(2)(3)

1st_order,

2nd_order,

3rd_order, or

disable

Specifies the DSM order for shifting the fractional noise to

be filtered out by the PLL to high frequencies.

Multiply Factor (M-

Counter)

(3)

1-512

Specifies the multiply factor of

M

-counter.

Fractional Multiply Factor

(K)

(2)(3)

1 to (2^

Fcout

-

1)

Specifies the fractional multiply factor of DSM.

Fcout

is the

value of fractional carry out parameter.

Divide Factor (N-

Counter)

(3)

1-512

Specifies the divide factor of

N

-counter.

Make this a cascade

counter

(3)(4)

Turn on or

Turn off

Turn on to cascade this counter into the next counter

output for larger division factor.

Divide Factor (C-

Counter)

(3)

1-512

Specifies the divide factor for the output clock (

C

-counter)

Altera PLL IP Core Parameters - Clock Switchover Tab

Table 2: Altera PLL IP Core Parameters - Clock Switchover Tab

Parameter

Legal Value

Description

Create a second input clk

‘refclk1’

Turn on or

Turn off

Turn on to provide a backup clock attached to your PLL

that can switch with your original reference clock.

(1)

This parameter is only available when Enable physical output clock parameters is turned off.

(2)

This parameter is only available in Fractional-N PLL mode.

(3)

This parameter is only available when Enable physical output clock parameters is turned on.

(4)

This feature is only supported in Quartus

®

II version 13.1 and onwards.

4

Altera PLL IP Core Parameters - Clock Switchover Tab

UG-01087

2015.05.04

Altera Corporation

Altera Phase-Locked Loop (Altera PLL) IP Core User Guide