Altera DSP Development Kit, Stratix V Edition User Manual

Page 21

Chapter 4: Development Board Setup

4–5

Factory Default Switch Settings

July 2013

Altera Corporation

DSP Development Kit, Stratix V Edition

User Guide

f

For more information, refer to

section in volume 2,

Chapter 9, of the Stratix V Device Handbook.

4. Set DIP switch bank (SW5) to match

1

If you use an external USB Blaster, Altera recommends that you disable the power-up

configuration of the FPGA by changing the MSEL(4:0) DIP switch (SW4) from 01000

to 11000. This will prevent power-up FPGA configuration from flash in the default

FPPx32 mode. The On-Board USB-Blaster II is disabled when you plug in an external

USB Blaster, which prevents the JTAG FACTORY command from being sent to disable

the security mode JTAG lockout prior to configuring the Stratix V. The On-Board

USB-Blaster II issues the JTAG FACTORY command when the SECURITY switch

(SW5.4) is set to 1. For more information on the Stratix V ES JTAG Port Access

Limitation After Configuration, refer to the

.

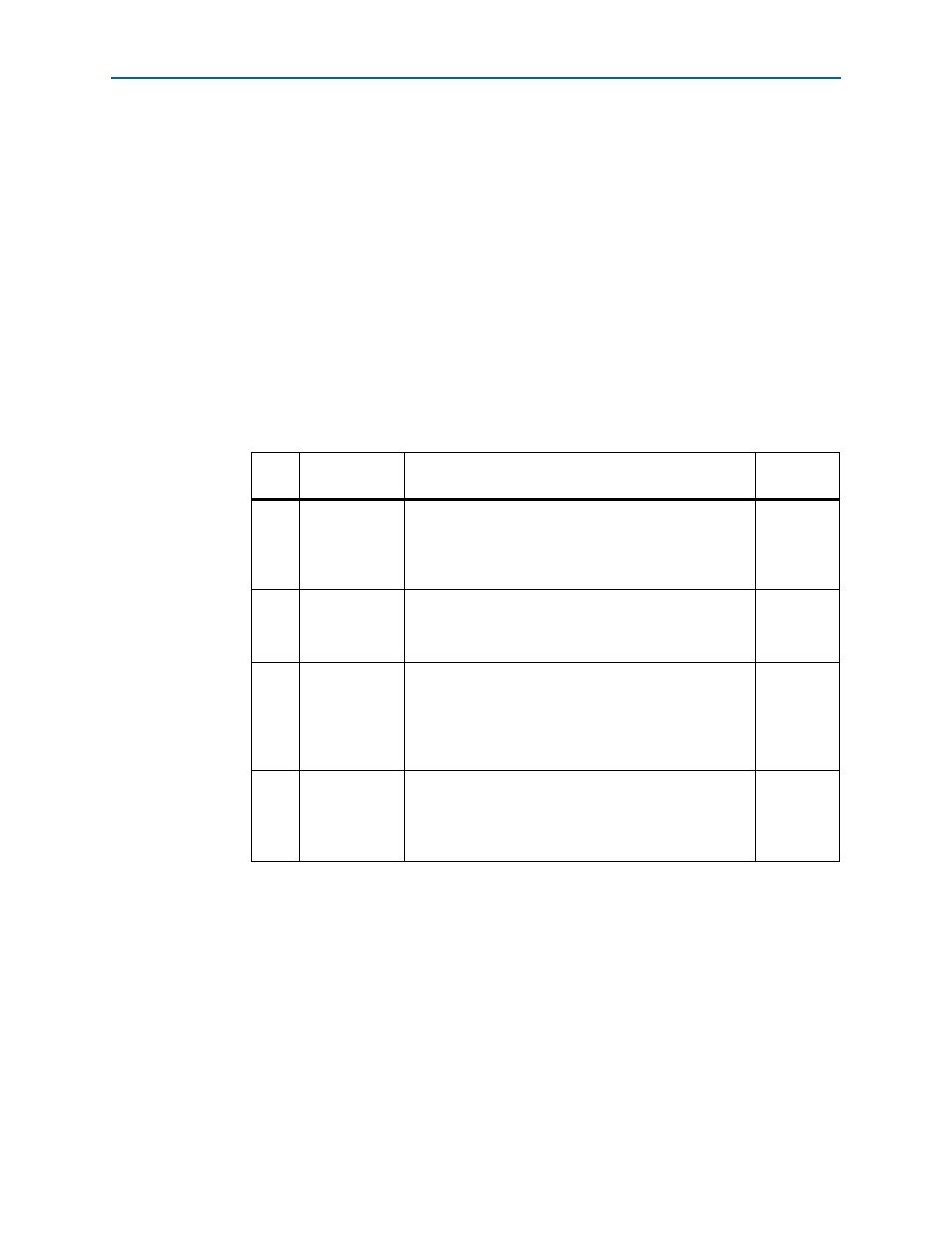

Table 4–4. SW5 DIP Switch Settings

Switc

h

Board

Label

Function

Default

Position

1

CLK_SEL

Switch 1 has the following options:

■

When on (0), the SMA input clock is selected.

■

When off (1), the programmable oscillator clock is

selected.

Off

2

CLK_EN

Switch 2 has the following options:

■

When on (0), the on-board oscillator is enabled.

■

When off (1), the on-board oscillator is disabled.

On

3

FACTORY

Switch 3 has the following options:

■

When on (0), loads the user design from flash at power

up.

■

When off (1), loads the factory design from flash at

power up.

Off

4

SECURITY

Switch 4 has the following options:

■

When on (0), does not send factory command at power

up.

■

When off (1), sends factory command at power up.

Off

Note to

:

(1) Functionality of the CLK_EN, FACTORY and SECURITY settings are dependent on the MAX V system controller

CPLD. In order to function properly, the MAX V CPLD must be programmed with the required MAX V design.