High speed differential interface (hsdi) – Altera PowerPlay Early Power Estimator User Manual

Page 36

3–22

Altera

Corporation

PowerPlay Early Power Estimator For Arria GX FPGAs

May 2008

PowerPlay Early Power Estimator Inputs

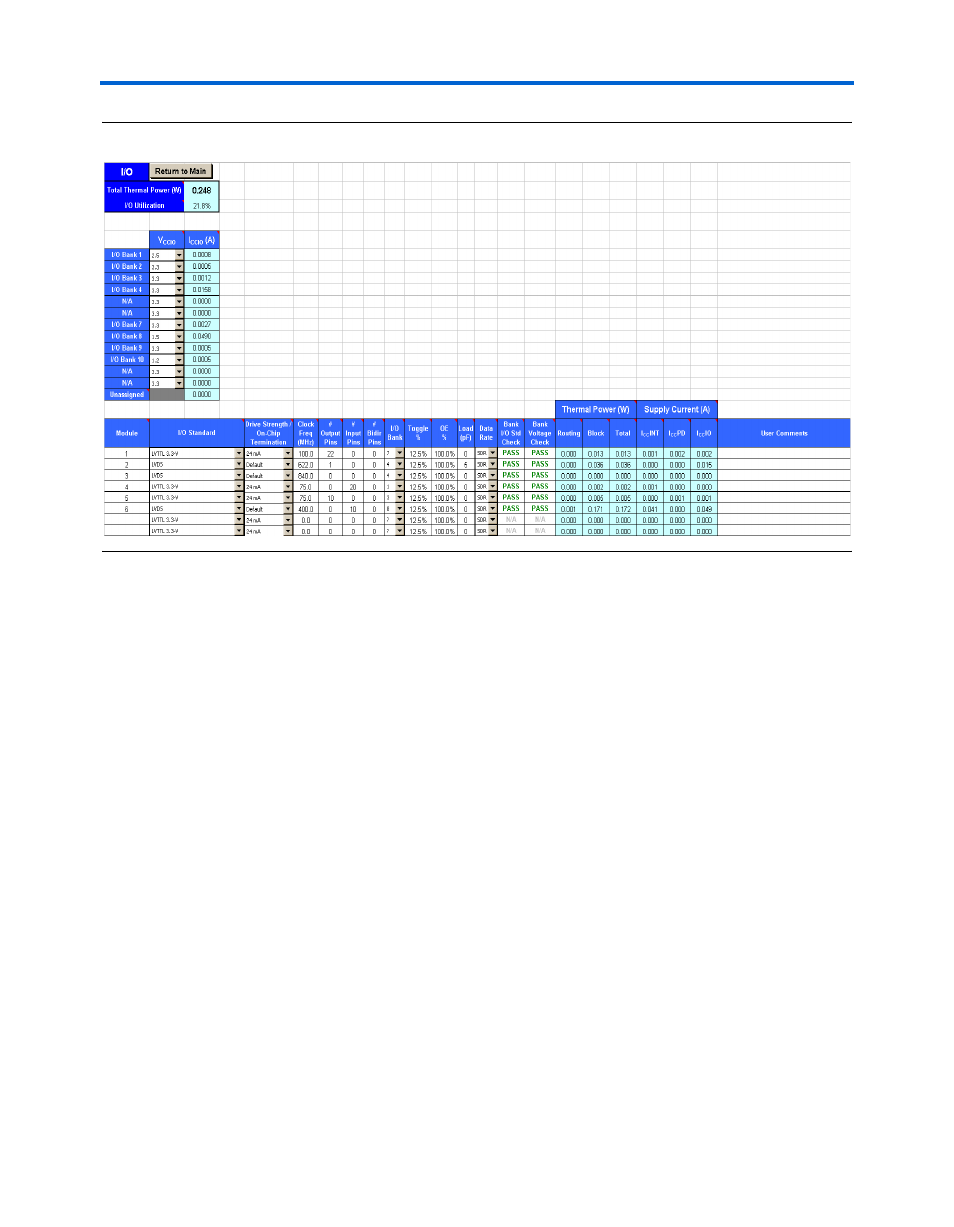

Figure 3–13. I/O Section in the PowerPlay Early Power Estimator

High Speed Differential Interface (HSDI)

Arria GX devices feature dedicated circuitry that interface with

high-speed differential I/O standards. These are dedicated transmitters

and receivers that contain serializer and deserializer blocks, respectively.

The HSDI section in the PowerPlay Early Power Estimator spreadsheet

is divided into to receiver and transmitter parts.

1

The power calculated in the HSDI section only applies to the

transmitter serializer block or the receiver deserializer block.

The transmitter and receiver are implemented using the

altlvds megafunction. The I/O buffer power is calculated in

the I/O section and the PLL power is calculated in the PLL

section.

Each row in the HSDI section represents a separate receiver or

transmitter domain. You must enter the following parameters for

transmitter and receiver domains:

■

Data rate (in Mbps)

■

Number of channels in that transmitter domain.

■

Toggle percentage

1

The receiver power is the same whether or not the DPA circuitry

is used.