Transceiver (xcvr), Figure 3–19, Shows – Altera PowerPlay Early Power Estimator User Manual

Page 42

3–28

Altera

Corporation

PowerPlay Early Power Estimator For Arria GX FPGAs

May 2008

PowerPlay Early Power Estimator Inputs

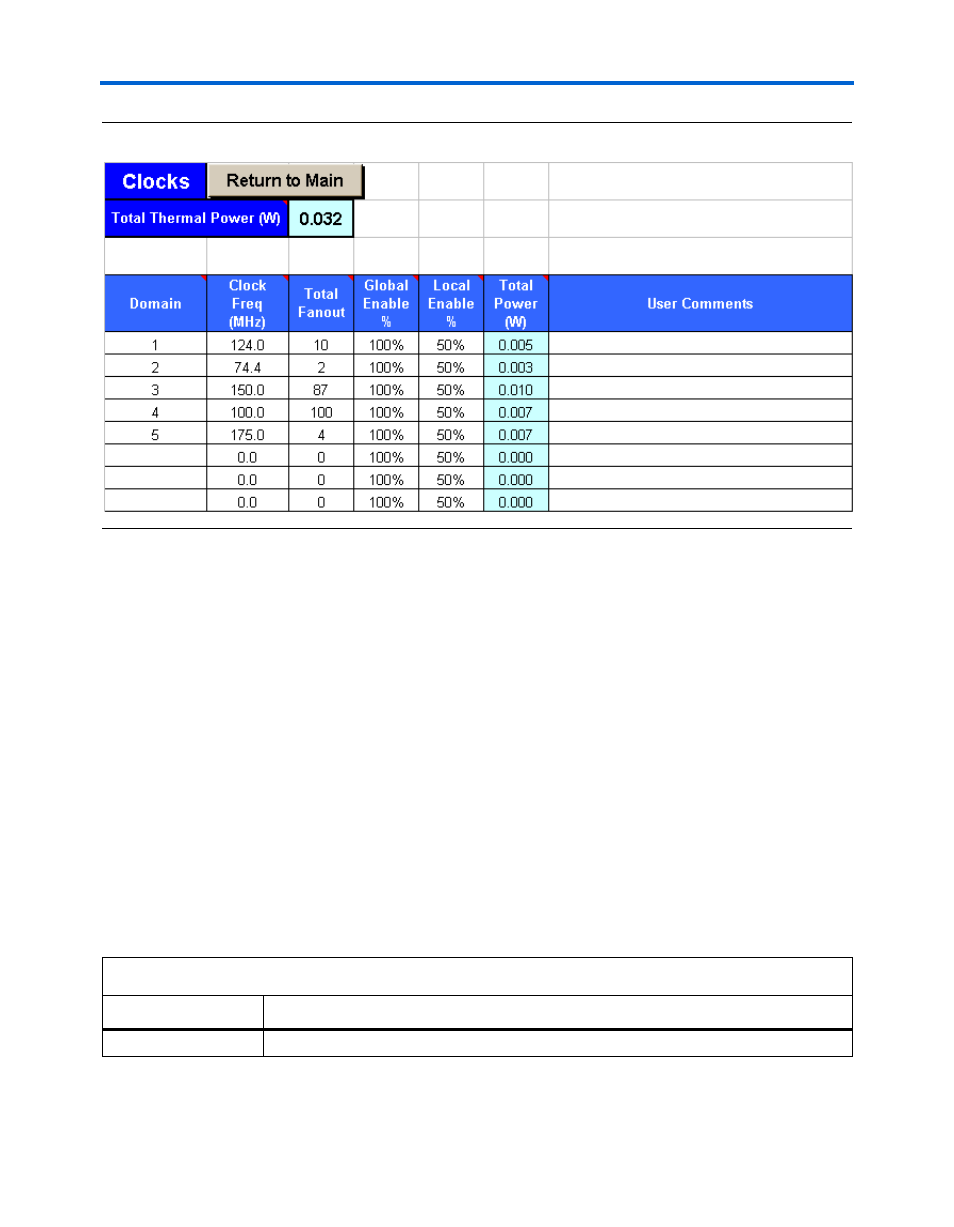

Figure 3–19. Clocks Section in the PowerPlay Early Power Estimator

Transceiver (XCVR)

Arria GX devices feature dedicated embedded circuitry on the right side

of the device that contain up to 12 high-speed 2.5 and 1.25 Gbps serial

transceiver channels. Arria GX devices have dedicated transmitters and

receivers that contain serializer and deserializer blocks, which support

PCI Express (PIPE) and Serial RapidIO

TM

protocols.

The power calculated in this section applies to the transceiver blocks,

including the channels used and all circuitry used in the Clock Control

Unit (CCU). The transceivers are implemented using the

ALT2GXB

megafunction. The I/O buffer power and the PLL power for the

transceivers are included in this section. Transmitters and receivers

assume 100

Ω termination.

There are six transceiver power rails: V

CCT

, V

CCH

, V

CCR

, V

CCA

, V

CCP,

and

V

CCL

.

Table 3–10

describes the information reported for each rail.

Table 3–10. Transceiver Power Supply Information in the I/O Section (Part 1 of 2)

Column Heading

Description

Power Rails

Power supply rails for the transceiver blocks.