Altera Stratix IV GT 100G User Manual

Page 19

Chapter 4: Development Board Setup

4–3

Factory Default Switch Settings

October 2010

Altera Corporation

Stratix IV GT 100G Development Kit User Guide

2. Set the User DIP Switch bank (SW3) and FPGA User DIP Switch bank (SW4) to the

1

position, as shown in

Figure 4–1

.

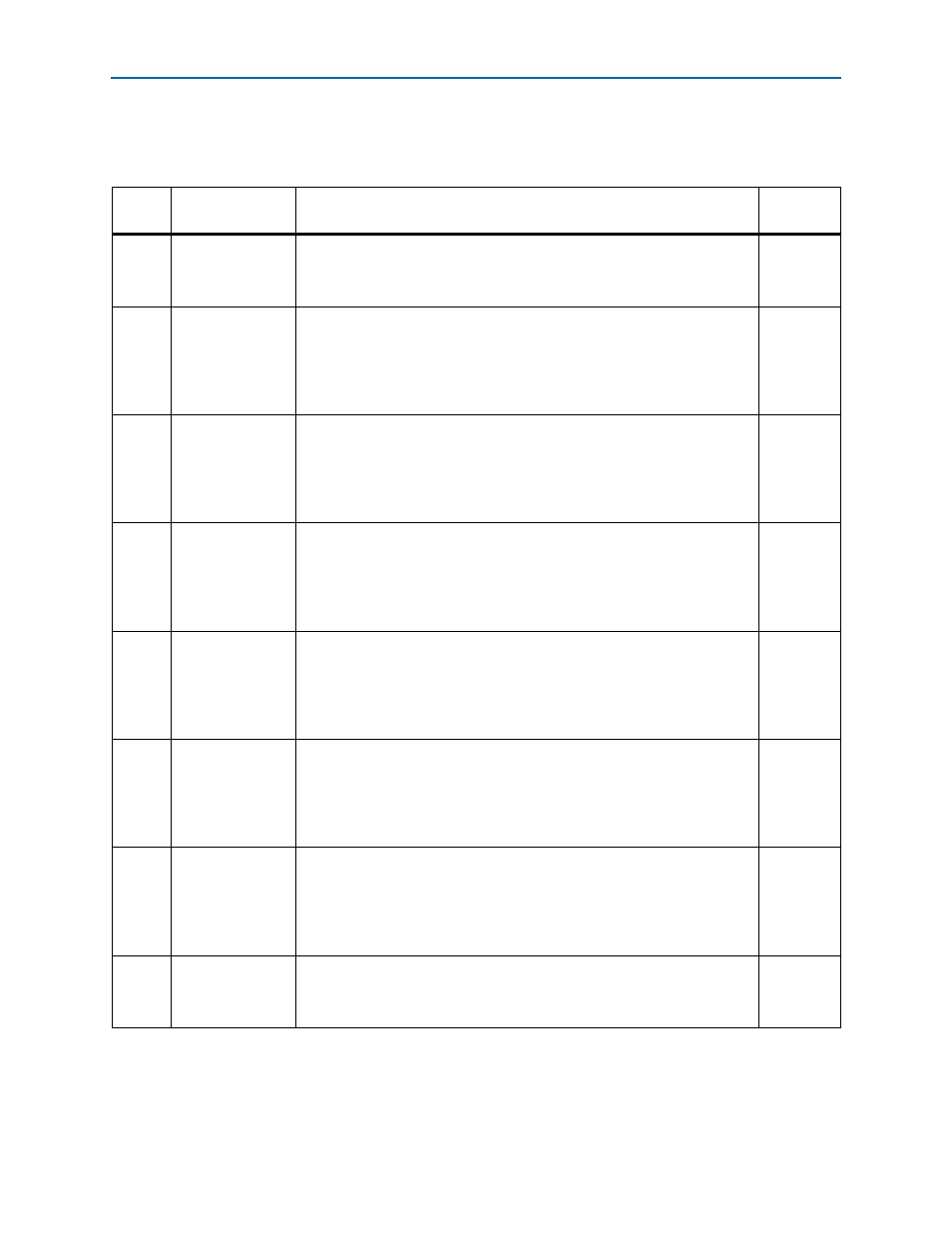

Table 4–1. SW2 Dip Switch Settings

Switch

Board

Label

Function

Default

Position

1

USB_DISABLEn

Switch 1 has the following options:

■

When on, a logic 1 is selected. Enables the Embedded USB Blaster.

■

When off, a logic 0 is selected. Disables the Embedded USB Blaster.

On

2

DIFFCLKA_SEL

Switch 2 has the following options:

■

When on, a logic 1 is selected. The PLL for the single ended clock goes to

the global clock inputs of the A tree structure.

■

When off, a logic 0 is selected. The SMA input for the single ended clock

goes to the global clock inputs of the A tree structure.

On

3

REFCLKA_SEL

Switch 3 has the following options:

■

When on, a logic 1 is selected. The PLL goes to the transceivers on the A

clock tree structure.

■

When off, a logic 0 is selected. The SMA input goes to the transceivers on

the A clock tree structure.

On

4

SE_CLKA_SEL

Switch 4 has the following options:

■

When on, a logic 1 is selected. The SMA for the single ended clock goes to

the global clock inputs of the A tree structure.

■

When off, a logic 0 is selected. The PLL for the single ended clock goes to

the global clock inputs of the A tree structure.

Off

5

DIFFCLKB_SEL

Switch 5 has the following options:

■

When on, a logic 1 is selected. The PLL for the single ended clock goes to

the global clock inputs of the B tree structure.

■

When on, a logic 1 is selected. The PLL for the single ended clock goes to

the global clock inputs of the B tree structure.

On

6

REFCLKB_SEL

Switch 6 has the following options:

■

When off, a logic 0 is selected. The PLL goes to the transceivers on the B

clock tree structure.

■

When on, a logic 1 is selected. The SMA goes to the transceivers on the B

clock tree structure.

Off

7

SE_CLKB_SEL

Switch 7 has the following options:

■

When on, a logic 1 is selected. The SMA for the single ended clock goes to

the global clock inputs of the B tree structure.

■

When off, a logic 0 is selected. The PLL for the single ended clock goes to

the global clock inputs of the B tree structure.

Off

8

CLK644_EN

Switch 8 has the following options:

■

When on, a logic 1 is selected. Enables the 644.53125MHz clock.

■

When off, a logic 0 is selected. Disables the 644.53125MHz clock.

On