Advanced chipset features, Bios setup – DFI ML905-B11C/B16C User Manual

Page 41

41

3

BIOS Setup

Advanced Chipset Features

This section gives you functions to configure the system based on the specific

features of the chipset. The chipset manages bus speeds and access to system

memory resources.

These items should not be altered unless necessary.

The

default settings have been chosen because they provide the best operating con-

ditions for your system. The only time you might consider making any changes

would be if you discovered some incompatibility or that data was being lost while

using your system.

DRAM Timing Selectable

This field is used to select the timing of the DRAM.

By SPD

The EEPROM on a DIMM has SPD (Serial Presence Detect) data structure that

stores information about the module such as the memory type, memory size,

memory speed, etc. When this option is selected, the system will run accord-

ing to the information in the EEPROM. This option is the default setting be-

cause it provides the most stable condition for the system. The “CAS Latency

Time” to “System Memory Frequency” fields will show the default settings by

SPD.

Manual

If you want better performance for your system other than the one “by SPD”,

select “Manual” then select the best option in the “CAS Latency Time” to

“System Memory Frequency” fields.

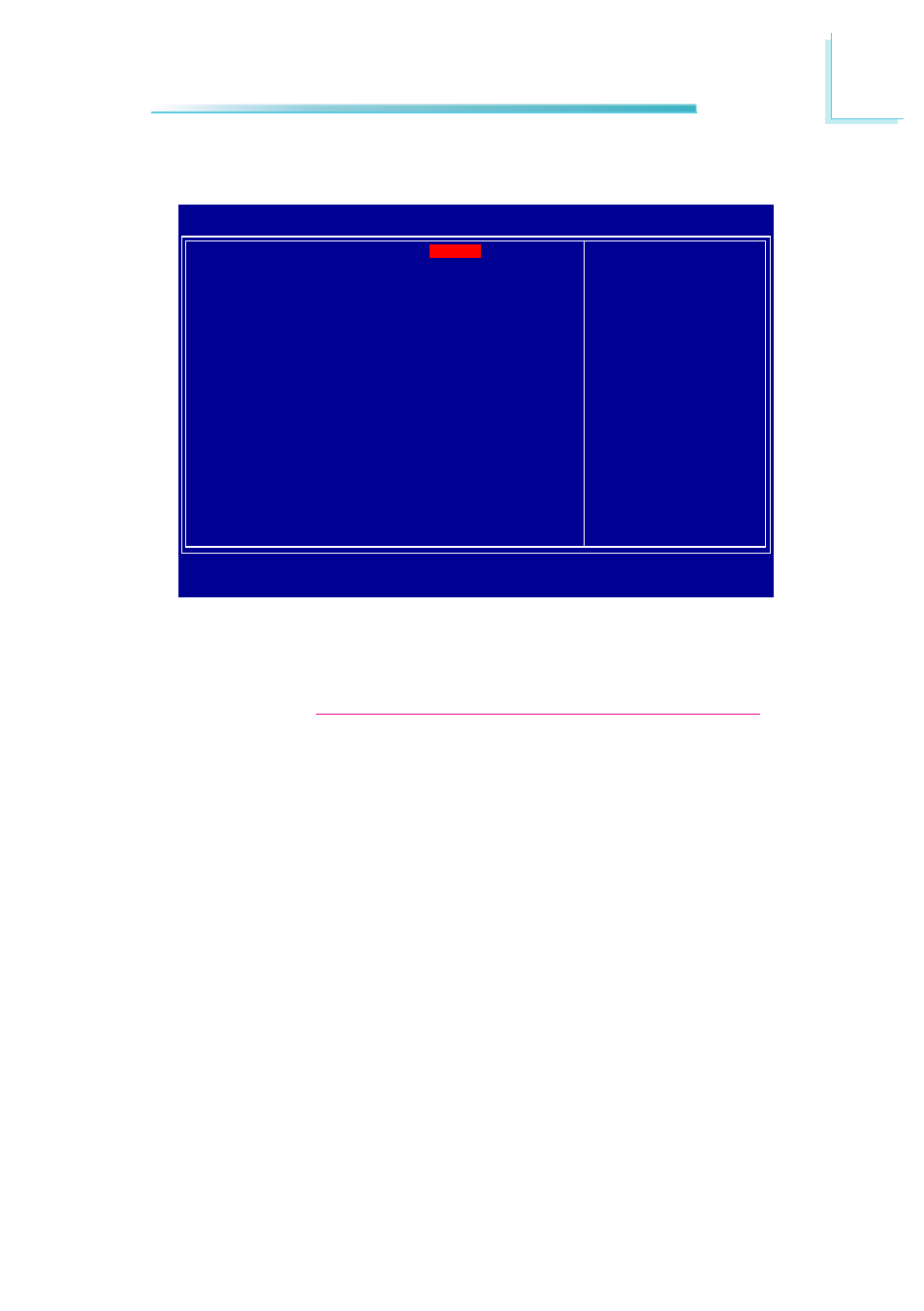

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

DRAM Timing Selectable

System BIOS Cacheable

Video BIOS Cacheable

** VGA Setting **

On-Chip Frame Buffer Size

Boot Type

LCD Panel Type

Item Help

Menu Level

By SPD

[Enabled]

[Disabled]

[8MB]

[SDVO]

[1 : 640*480 (18b it)]

↑↓→←

: Move

Enter: Select

F1: General Help

+/-/PU/PD: Value

F10: Save

ESC: Exit

F5: Previous Values

F6: Fail-Safe Defaults

F7: Optimized Defaults

The settings on the screen are for reference only. Your version may not be identical to

this one.