Altera Floating-Point User Manual

Page 145

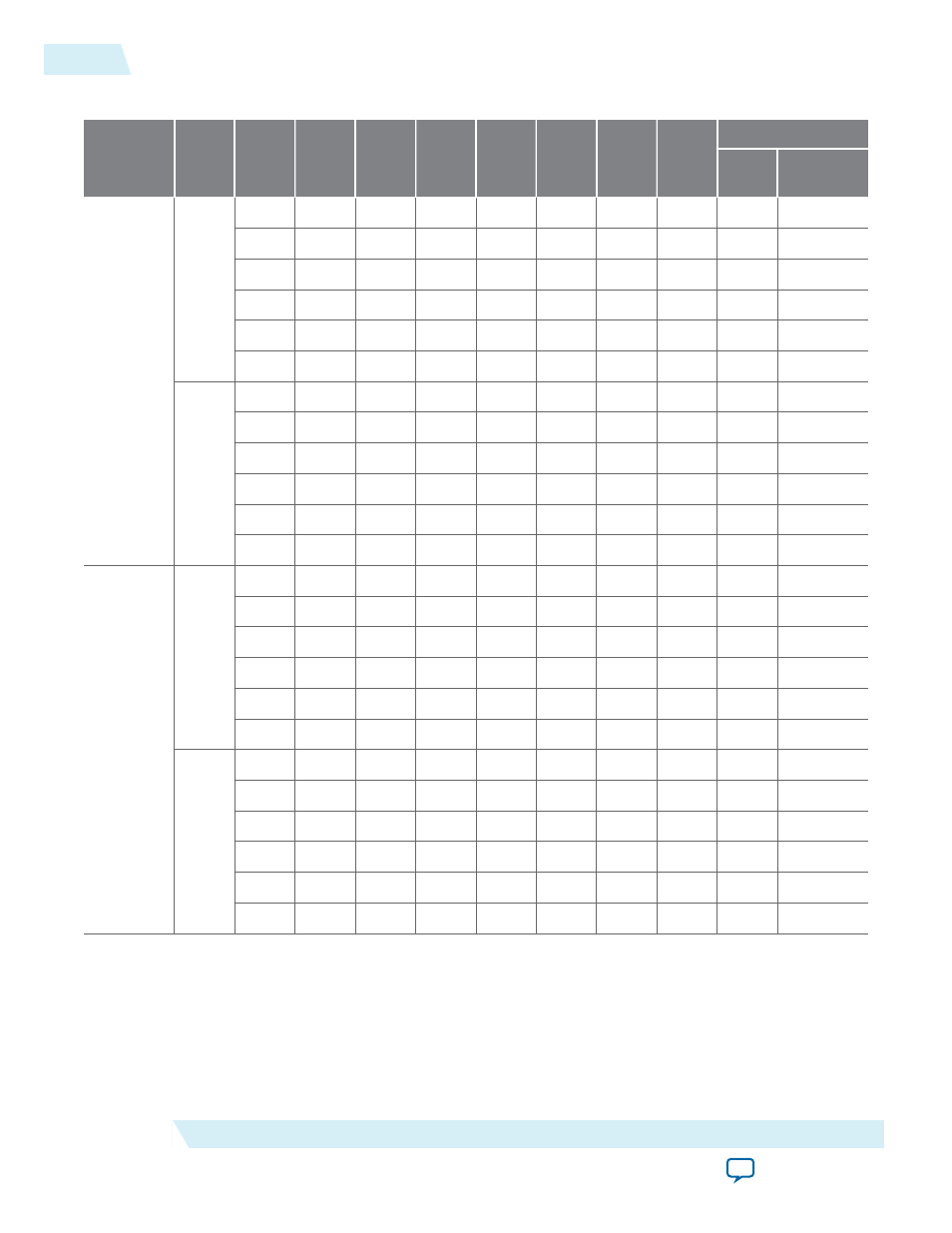

Table 18-4: FPFXP

Family

Input

Precisi

on

Output

Width

Output

Fractio

n

Latenc

y

f

MAX

ALMs

M10K

M20K

DSP

Blocks

Logic Registers

Primar

y

Secondary

Arria V

(5AGXFB3

H4F40C5)

Single

32

0

2

277.93

168

0

--

0

75

1

32

16

2

266.1

169

0

--

0

75

0

32

32

2

277.93

168

0

--

0

75

1

64

0

3

226.4

291

0

--

0

172

0

64

16

3

226.4

291

0

--

0

172

0

64

32

3

226.4

291

0

--

0

172

0

Doubl

e

32

0

3

332.12

197

0

--

0

115

0

32

16

3

344.12

197

0

--

0

115

0

32

32

3

332.12

197

0

--

0

115

0

64

0

3

256.28

326

0

--

0

205

4

64

16

3

256.28

326

0

--

0

205

4

64

32

3

256.28

326

0

--

0

205

4

Cyclone V

(5CGXFC7

D6F31C7)

Single

32

0

3

245.04

171

0

--

0

110

0

32

16

3

245.04

171

0

--

0

110

0

32

32

3

245.04

171

0

--

0

110

0

64

0

4

190.62

244

0

--

0

269

0

64

16

4

190.62

244

0

--

0

269

0

64

32

4

190.62

244

0

--

0

269

0

Doubl

e

32

0

4

291.63

209

0

--

0

160

1

32

16

4

302.94

209

0

--

0

160

1

32

32

4

291.63

209

0

--

0

160

1

64

0

5

207.25

329

0

--

0

347

2

64

16

5

207.25

329

0

--

0

347

2

64

32

5

207.25

329

0

--

0

347

2

18-18

ALTERA_FP_FUNCTIONS Resource Utilization and Performance

UG-01058

2014.12.19

Altera Corporation

ALTERA_FP_FUNCTIONS IP Core