Altera Floating-Point User Manual

Page 83

ALTFP_INV Design Example: Understanding the Simulation Results

The simulation waveform in this design example is not shown in its entirety. Run the design example files

in the ModelSim-Altera software to see the complete simulation waveforms.

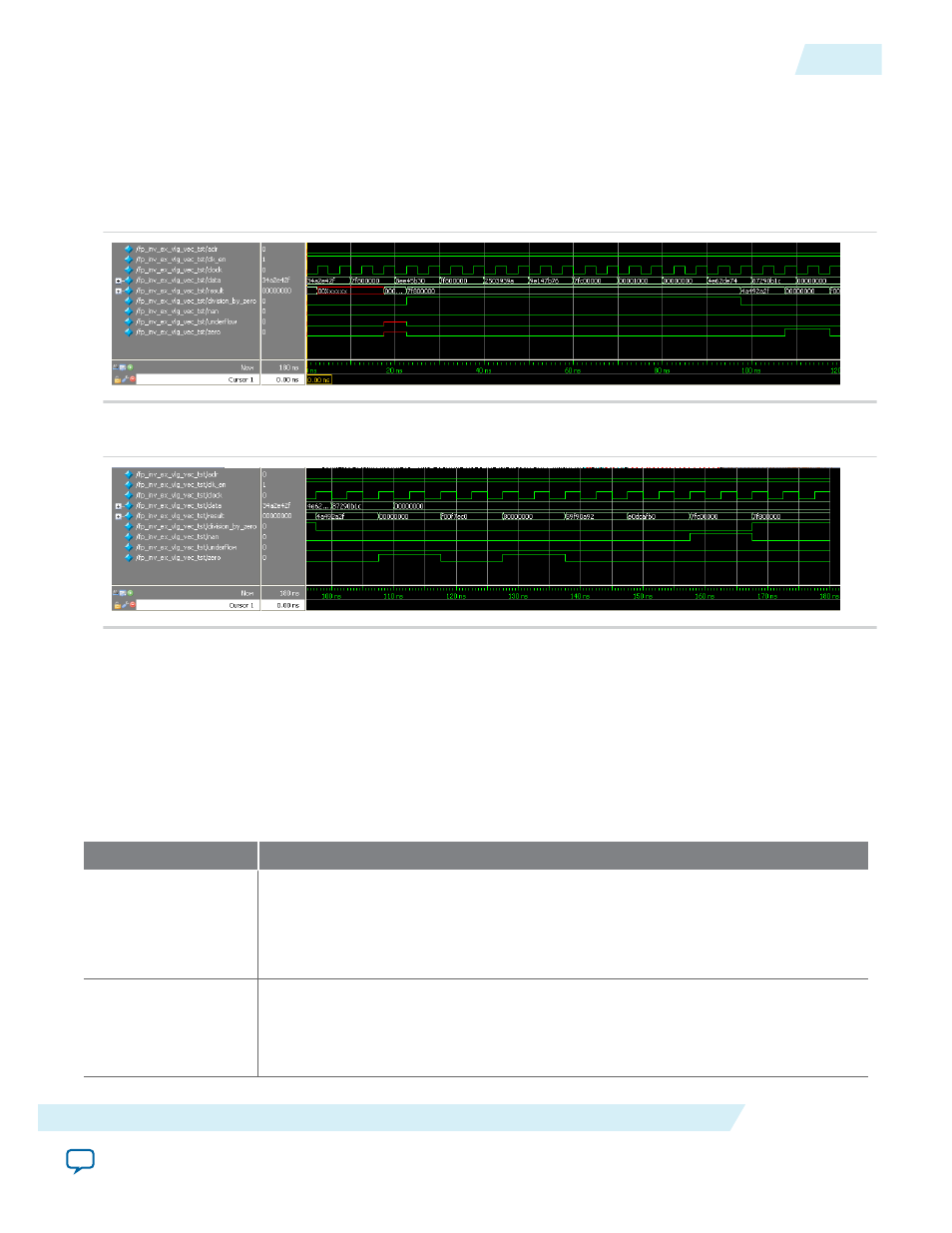

These figures show the expected simulation results in the ModelSim-Altera software.

Figure 10-1: ALTFP_INV ModelSim Simulation Waveform (Input Data)

Figure 10-2: ALTFP_INV ModelSim Simulation Waveform (Output Data)

This design example implements a floating-point inverse for single-precision format numbers. The

optional input ports (

clk_en

and

aclr

) and all four exception handling output ports (

division_by_zero

,

nan

,

zero

, and

underflow

) are enabled.

The latency is fixed at 20 clock cycles; therefore, every inverse operation outputs results 20 clock cycles

later.

This table lists the inputs and corresponding outputs obtained from the simulation in the waveforms.

Table 10-3: Summary of Input Values and Corresponding Outputs

Time

Event

0 ns, start-up

data[]

value: 34A2 E42Fh

Output value: An undefined value is seen on the

result[]

port, which is ignored.

All values seen on the output port before the 20th clock cycle are merely due to the

behavior of the system during start-up and should be disregarded.

97.5 ns

Output value: 4A49 2A2Fh

Exception handling ports:

division_by_zero

deasserts

The inverse of a normal number results in a normal value.

UG-01058

2014.12.19

ALTFP_INV Design Example: Understanding the Simulation Results

10-3

ALTFP_INV IP Core

Altera Corporation