Altera Cyclone III LS FPGA Development Board User Manual

Page 17

Chapter 2: Board Components

2–9

MAX II CPLD EPM2210 System Controller

© October 2009 Altera Corporation

Cyclone III LS FPGA Development Board Reference Manual

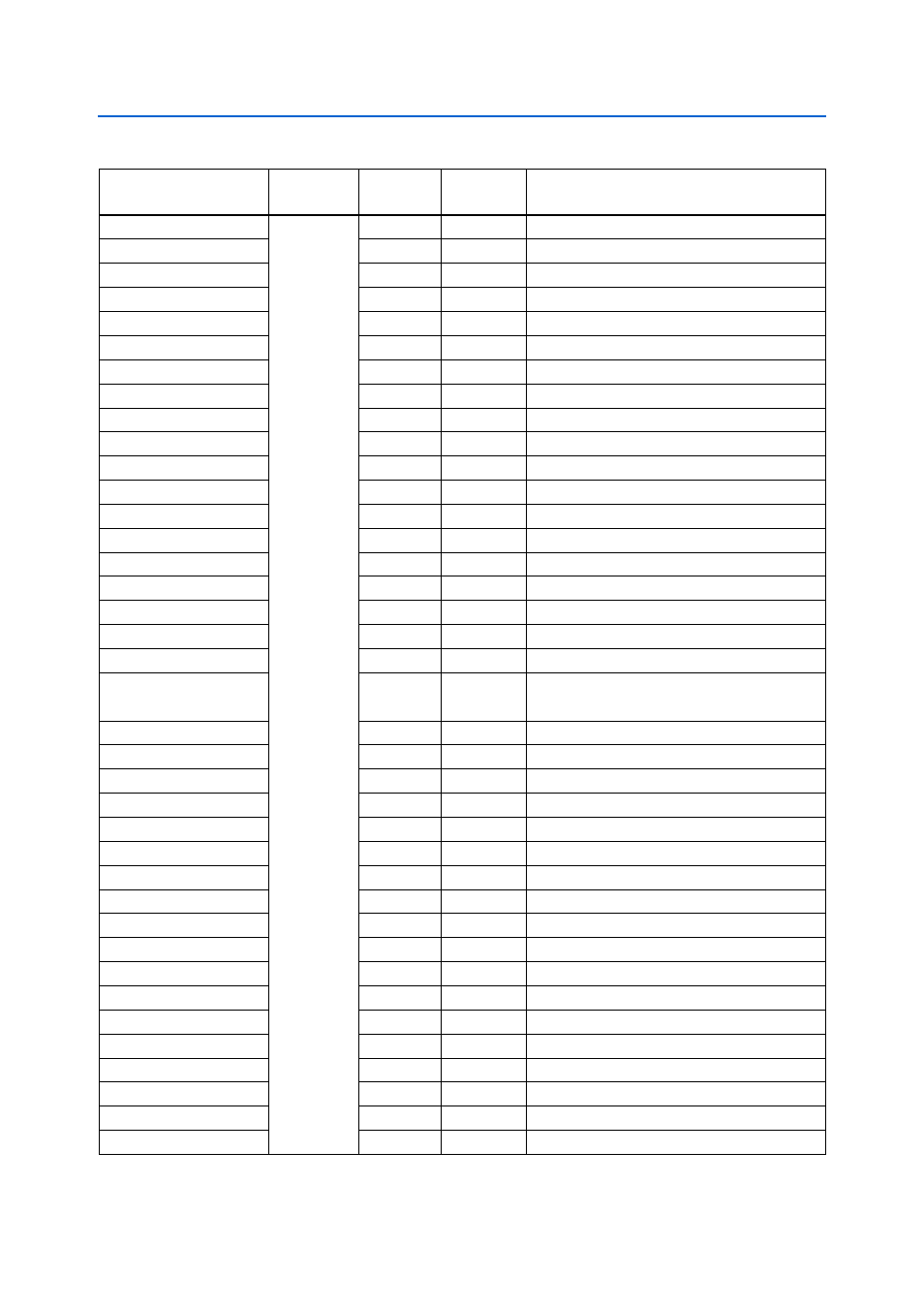

FSM_D16

2.5-V

N9

AH20

FSM bus data

FSM_D17

T8

AH18

FSM bus data

FSM_D18

T9

AF8

FSM bus data

FSM_D19

R9

AE20

FSM bus data

FSM_D20

P9

AB19

FSM bus data

FSM_D21

T10

AB10

FSM bus data

FSM_D22

M10

AC17

FSM bus data

FSM_D23

T11

AD10

FSM bus data

FSM_D24

N10

AG9

FSM bus data

FSM_D25

R11

AE21

FSM bus data

FSM_D26

P10

AD22

FSM bus data

FSM_D27

T12

AH23

FSM bus data

FSM_D28

M11

AG5

FSM bus data

FSM_D29

R12

AB9

FSM bus data

FSM_D30

N11

AD9

FSM bus data

FSM_D31

T13

AD16

FSM bus data

HEARTBEAT

M1

AH7

Anti-Tamper FPGA general I/O

HSMA_PRSNTn

J16

—

HSMC port A present

HSMB_PRSNTn

J13

—

HSMC port B present

JTAG_AT_SEL

K16

—

Jumper OFF (default): Select JTAG chain

Jumper ON: MAX II controls FPGA JTAG

JTAG_SECURE

R5

—

DIP - JTAG security mode ON/OFF

M2Z_CONF_DONE

R13

—

On-board USB-Blaster FPGA configuration done

M2Z_D0

T15

—

On-board USB-Blaster FPGA configuration data

M2Z_DCLK

N12

—

On-board USB-Blaster FPGA configuration clock

M2Z_nCONFIG

R14

—

On-board USB-Blaster FPGA configuration active

M2Z_nSTATUS

M12

—

On-board USB-Blaster FPGA configuration ready

MAX2_BEn0

F5

AG21

FSM bus MAX II byte enable 0

MAX2_BEn1

F2

AF11

FSM bus MAX II byte enable 1

MAX2_BEn2

F6

AG2

FSM bus MAX II byte enable 2

MAX2_BEn3

F1

AC16

FSM bus MAX II byte enable 3

MAX2_CLK

E1

AE24

FSM bus MAX II clock

MAX2_CSn

E2

AG4

FSM bus MAX II chip select

MAX2_OEn

F3

AC10

FSM bus MAX II output enable

MAX2_WEn

F4

AA8

FSM bus MAX II write enable

MAX_CONF_DONE

E15

—

FPGA configuration done LED

MAX_DIP0

F16

—

DIP - Anti-Tamper example design

MAX_DIP1

G13

—

DIP - Anti-Tamper example design

AT_ACTIVE

F15

—

DIP - Anti-Tamper example design ON/OFF

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 3 of 4)

Schematic Signal Name

I/O Standard

EPM2210

Pin Number

EP3CLS200

Pin Number

Description