Interface, A.3.3 interface – Comtech EF Data SNM-1002 User Manual

Page 134

SNM-1002 LinkSync

Modem

Revision 2

Remote Control Operation

MN/SNM1002.OM

A–8

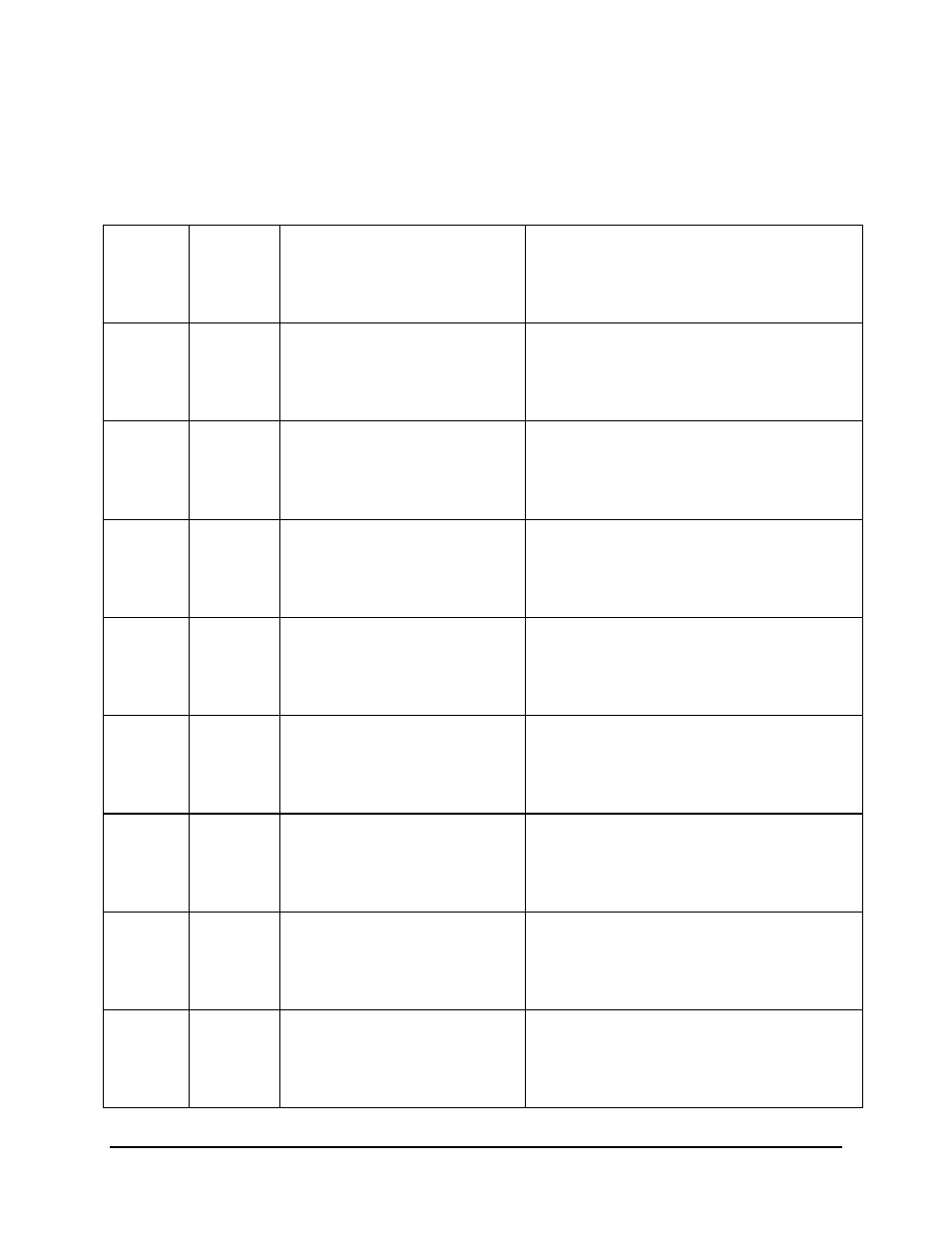

A.3.3 Interface

Interface

Transmit

Overhead

Type

Command:

Response:

Status:

Response:

<add/ITOT_xxxxx'cr'

>add/ITOT_xxxxx'cr''lf']

<add/ITOT_'cr'

>add/ITOT_xxxxx'cr''lf']

Where: xxxxx = NONE

Interface

Receive

Overhead

Type

Command:

Response:

Status:

Response:

<add/IROT_xxxxx'cr'

>add/IROT_xxxxx'cr''lf']

<add/IROT_'cr'

>add/IROT_xxxxx'cr''lf']

Where: xxxxx = NONE

TX Driver

Type

Command:

Response:

Status:

Response:

<add/TXDR_xxxxx'cr'

>add/TXDR_xxxxx'cr''lf']

<add/TXDR_'cr'

>add/TXDR_xxxxx'cr''lf']

Where: xxxxx = V35, RS422, or RS232.

RX Driver

Type

Command:

Response:

Status:

Response:

<add/RXDR_xxxxx'cr'

>add/RXDR_xxxxx'cr''lf']

<add/RXDR_'cr'

>add/RXDR_xxxxx'cr''lf']

Where: xxxxx = V35, RS422, or RS232.

Transmit

Clock

Command:

Response:

Status:

Response:

<add/TC_xxx'cr'

>add/TC_xxx'cr''lf']

<add/TC_'cr'

>add/TC_xxx'cr''lf']

Where: xxx = INT (internal SCT clock), EXT

(external TX terrestrial clock), REF (external clock-

reference frequency).

External

Clock-

Reference

Frequency

Command:

Response:

Status:

Response:

<add/ERF_nnnnn.n'cr'

>add/ERF_nnnnn.n'cr''lf']

<add/ERF_'cr'

>add/ERF_nnnnn.n'cr''lf']

Where: nnnnn.n = 8.0 to 10000.0 (external clock

frequency in kHz).

Transmit

Clock

Phase

Command:

Response:

Status:

Response:

<add/TCP_xxxx'cr'

>add/TCP_xxxx'cr''lf']

<add/TCP_'cr'

>add/TCP_xxxx'cr''lf']

Where: xxxx = NRM (normal clock phasing), INV

(inverted clock phasing), AUTO (automatic clock

phasing).

Buffer

Clock

Command:

Response:

Status:

Response:

<add/BC_xxx'cr'

>add/BC_xxx'cr''lf']

<add/BC_'cr'

>add/BC_xxx'cr''lf']

Where: xxx = INT (internal SCT clock), EXT

(external TX terrestrial clock), SAT (receive satellite

clock), REF (external clock-reference frequency),

INS (insert clock).

Receive

Clock

Phase

Command:

Response:

Status:

Response:

<add/RCP_xxx'cr'

>add/RCP_xxx'cr''lf']

<add/RCP_'cr'

>add/RCP_xxx'cr''lf']

Where: xxx = NRM (normal clock phasing), INV

(inverted clock phasing).