Max cpuid value limit, Execute-disable bit capability, Hyper threading technology – IBASE IB893 User Manual

Page 31: Intel speedstep(tm) tech (pineview-m), Intel(r) c-state tech, Enhanced c-states

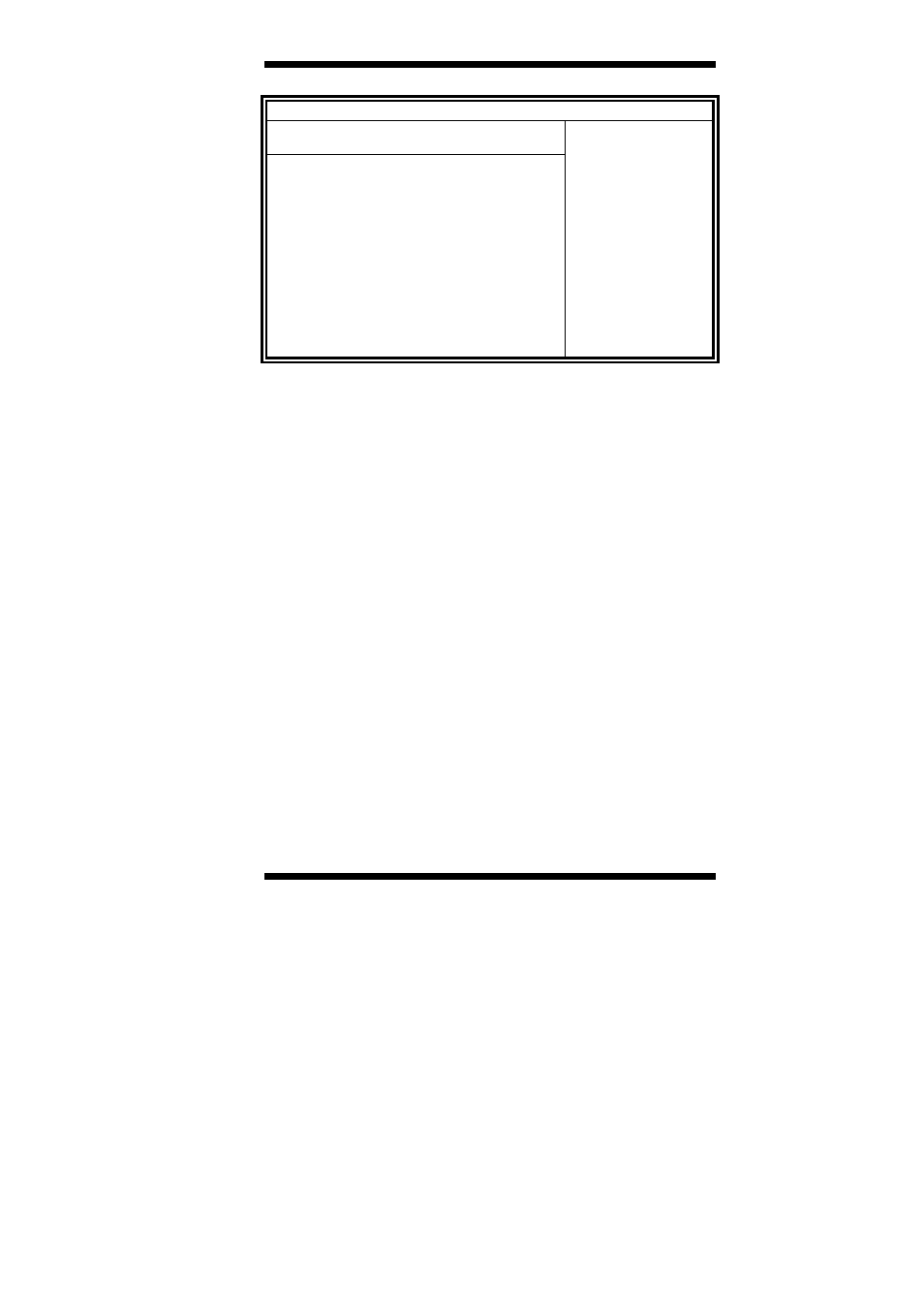

BIOS SETUP

IB893 User’s Manual

27

BIOS SETUP UTILITY

Advanced

Configure advanced CPU settings

Module Version:3F.18

Disabled for WindowsXP

<- Select

Screen

↑↓ Select

Item

+- Change Option

F1 General

Help

F10 Save and Exit

ESC Exit

Manufacturer: Intel

Intel(R) Atom (TM) CPU D525

@ 1.80GHz

Frequency :

1.80GHz

FSB Speed

: 800MHz

Cache L1

: 48KB

Cache L2

: 1024KB

Ratio Actual Value

: 9

Max CPUID Value Limit

[Disabled]

Execute-Disable Bit Capability [Enabled]

Hyper Threading Technology

[Enabled]

Intel(R) SpeedStep(tm) tech

Intel(R) C_STATE tech

Enhanced C-States

[Disabled]

[Enabled]

[Enabled]

The CPU Configuration menu shows the following CPU details:

Manufacturer: the name of the CPU manufacturer

Brand String: the brand name of the CPU being used

Frequency: the CPU processing speed

FSB Speed: the FSB speed

Cache L1: the CPU L1 cache size; Cache L2: the CPU L2 cache

Max CPUID Value Limit

Disabled for WindowsXP.

Execute-Disable Bit Capability

XD can prevent certain classes of malicious buffer overflow attacks when

combined with a supporting OS.

Hyper Threading Technology

Enabled for Windows XP and Linux (OS optimized for Hyper-Threading

Technology) and Disabled for other OS (OS not optimized for Hyper-Threading

Technology). When Disabled, only one thread per enabled core is enabled.

Intel SpeedStep(tm) tech (Pineview-M)

Disabled: Disable GV3

Enabled: Enable GV3

Intel(R) C-STATE tech

CState:CPU idle is set to C2 C3 C4 State

Enhanced C-States

CState:CPU idle is set to Enhanced C-States.

[