A. programming flash memory, Cfi flash memory, Cfi flash memory map – Altera Arria V SoC User Manual

Page 41: Appendix a. programming flash memory

June 2014

Altera Corporation

Arria V SoC Development Kit

User Guide

A. Programming Flash Memory

This appendix describes programming information for the following memory

devices:

■

Common flash interface (CFI) flash memory

■

Quad serial peripheral interface (quad SPI) flash memory

■

SD card flash memory

The Arria V development board’s flash memory comes preconfigured with the

parallel flash loader (PFL) option bits to support FPGA designs to be written to any of

the three locations (

). The PFL is disabled by default. Set SW2.3 to ON to

enable FPGA programming from CFI flash memory on power up.

1

There are several other factory software files written to flash memory to support the

Board Update Portal. These software files were created using the Nios II EDS, just as

the hardware design was created using the Quartus II software.

CFI Flash Memory

CFI Flash Memory Map

shows the default memory contents of the 512-Mb CFI flash device. For the

Board Update Portal to run correctly and update designs in the user memory, this

memory map must not be altered.

c

Altera recommends that you do not overwrite the factory hardware images unless

you are an expert with Altera tools. If you unintentionally overwrite the factory

hardware or factory software image, refer to

“Restoring the CFI Flash Device to the

Programming CFI Flash Using the Quartus II Programmer

You can use the JTAG interface in Altera CPLDs to indirectly program the flash

memory device. The Altera CPLD JTAG block interfaces directly with the logic array

in a special JTAG mode. This mode brings the JTAG chain through the logic array

instead of the Altera CPLD boundary-scan cells (BSC). The PFL megafunction

provides JTAG interface logic to do the following:

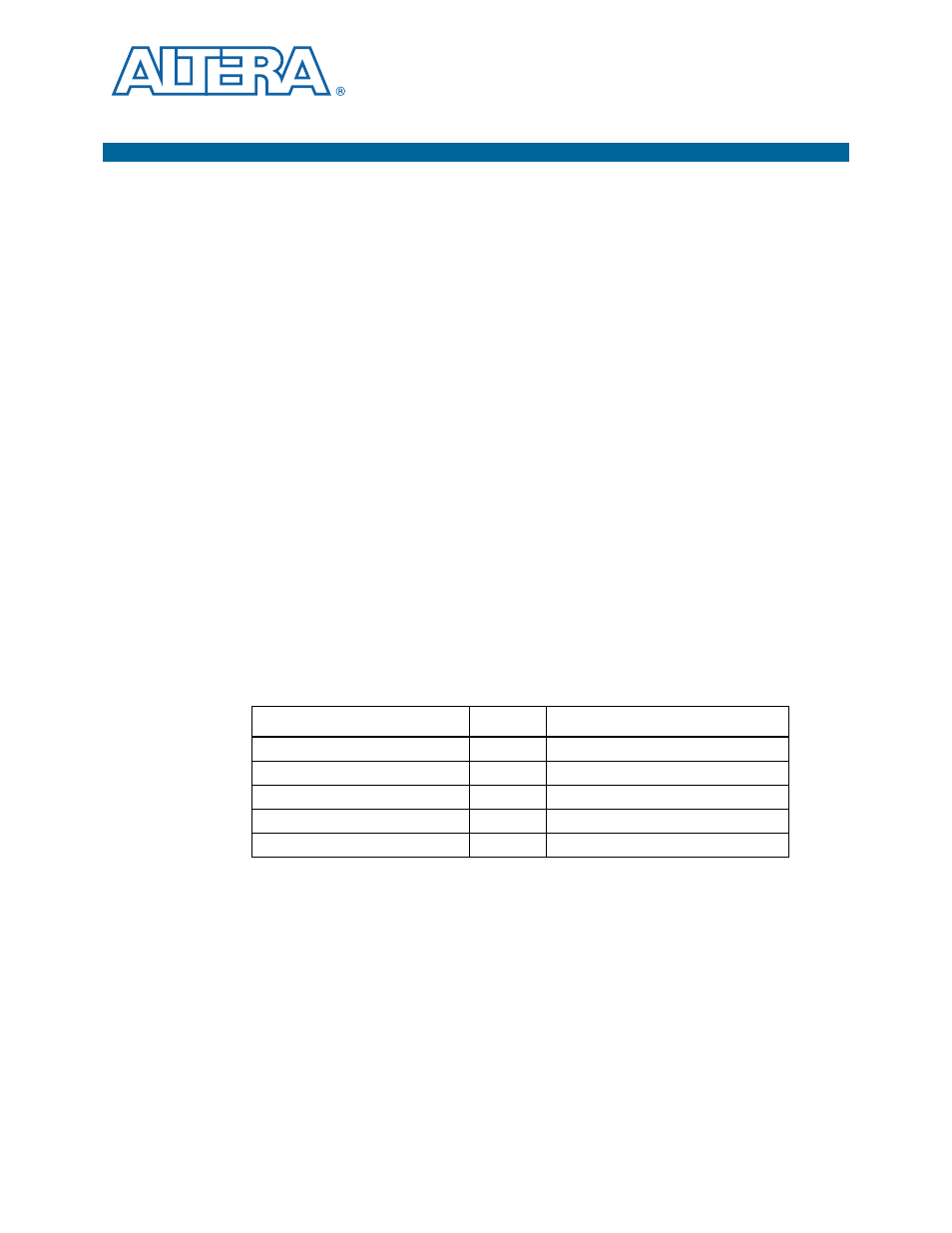

Table A–1. Byte Address Flash Memory Map

Block Description

KB Size

Address Range

Unused

20316

0x02CA.0000 - 0x03FF.FFFF

User hardware 1

23330

0x0166.0000 - 0x02C9.FFFF

Factory hardware (GHRD)

23330

0x0002.0000 - 0x0165.FFFF

PFL option bits

32

0x0001.8000 - 0x00019FFF

Reset vector

96

0x0000.0000 - 0001.7FFFF