Logic, Logic –4 – Altera PowerPlay Early Power Estimator User Manual

Page 16

3–4

Chapter 3: Using Cyclone III PowerPlay Early Power Estimator

PowerPlay Early Power Estimator Inputs

PowerPlay Early Power Estimator User Guide for Cyclone III FPGAs

© June 2009 Altera Corporation

Logic

A design is a combination of several design modules operating at different

frequencies and toggle rates. Each design module can have a different amount of

logic. For the most accurate power estimation, partition the design into different

design modules. You can partition your design by grouping modules by clock

frequency, location, hierarchy, or entities.

Each row in the Logic section represents a separate design module. You must enter

the following parameters for each design module:

■

Number of combinational look-up tables (LUTs)

■

Number of registers (FFs)

■

Clock frequency (f

MAX

) in MHz

■

Toggle percentage

Table 3–2

describes the values that must be specified in the Logic section of the

PowerPlay Early Power Estimator.

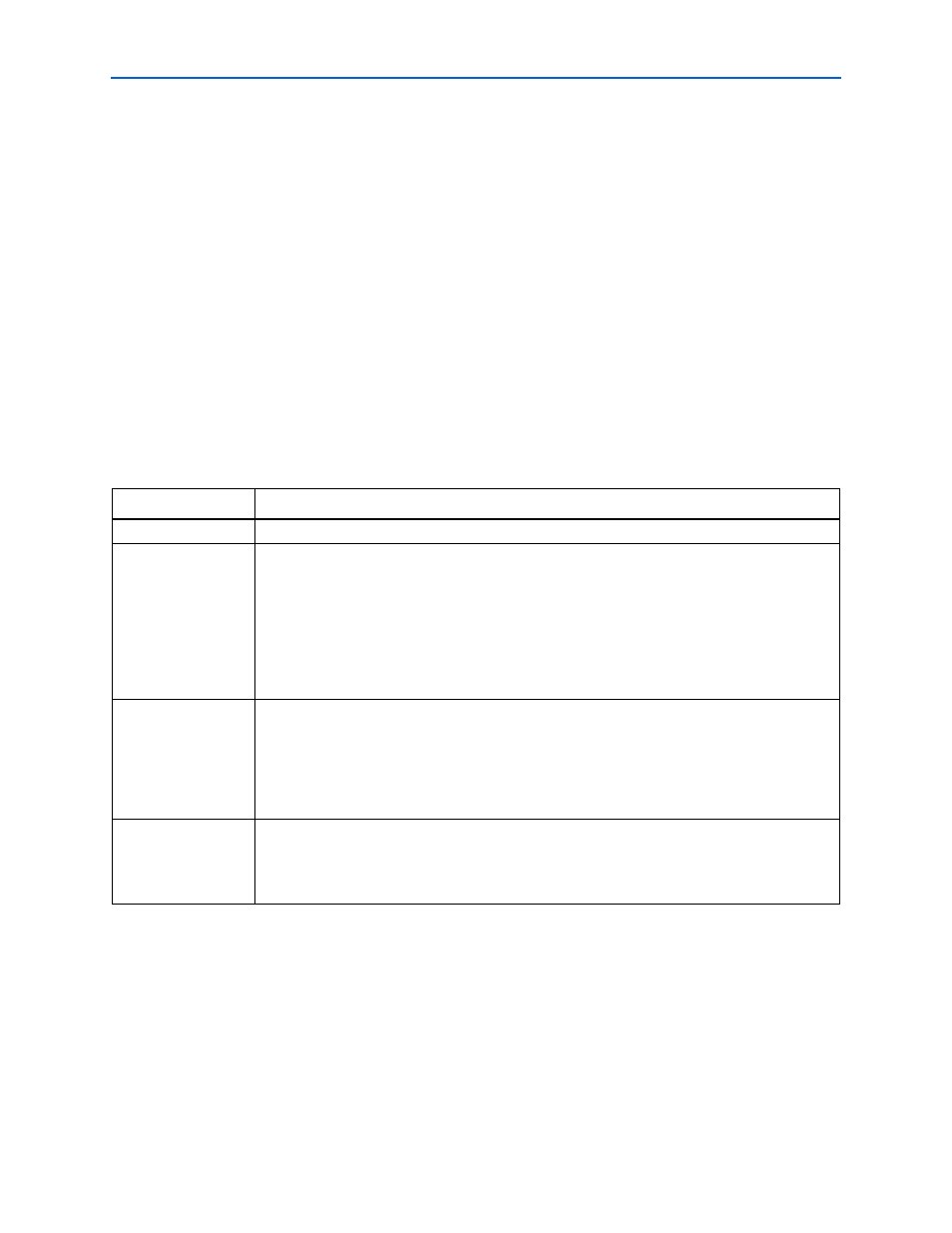

Table 3–2. Logic Section Information (Part 1 of 2)

Parameter

Description

Module

Enter a name for each module of the design. This is an optional value.

# LUTs

Enter the number of LUTs used in the whole design as reported in the Quartus II software

Compilation Report in the Fitter > Resource Section > Resource Usage Summary section.

For the number of LUTs to use, add the values from the following rows in the Fitter Resource Usage

Summary:

■

4 input functions

■

3 input functions

■

2 input functions

# FFs

Enter the number of registers used in the whole design as reported in the Quartus II software

Compilation Report. The number of registers used in Cyclone III device family is reported in the

Dedicated logic registers row in the Resource Usage Summary. To get to the Resource Usage

Summary, under Fitter open Resource Section and select Resource Usage Summary.

Clock routing power is calculated separately on the Clocks section of the PowerPlay Early Power

Estimator.

Clock Freq (MHz)

Enter a clock frequency for the module in MHz. This value is limited by the maximum frequency

specification for the device family.

100 MHz with a 12.5% toggle means that each LUT or flip-flop output toggles 12.5 million times

per second (100 × 12.5%).