Estimating power after completing the fpga design – Altera PowerPlay Early Power Estimator User Manual

Page 9

Chapter 2: Setting Up Cyclone III PowerPlay Early Power Estimator

2–3

Estimating Power

© June 2009 Altera Corporation

PowerPlay Early Power Estimator User Guide for Cyclone III FPGAs

Table 2–2

shows the advantages and disadvantages of using the PowerPlay Early

Power Estimator for an FPGA design that is partially complete.

Use the following steps to estimate power usage with the PowerPlay Early Power

Estimator if your FPGA design is partially complete:

1. Compile the partial FPGA design in the Quartus II software.

2. Generate the PowerPlay Early Power Estimator file (<revision

name>_early_pwr.csv) in the Quartus II software by clicking Generate PowerPlay

Early Power Estimator File

on the Project menu.

3. Download the PowerPlay Early Power Estimator from the Altera website on the

page.

4. Import the PowerPlay Early Power Estimator file into the PowerPlay Early Power

Estimator to automatically populate the entries.

5. After importing the file to populate the PowerPlay Early Power Estimator, you can

manually edit the cells to reflect the final device resource estimates.

Estimating Power After Completing the FPGA Design

When you complete your FPGA design, the PowerPlay Power Analyzer in the

Quartus II software provides the most accurate power consumption estimate of your

device. In addition to place-and-route information, the PowerPlay Analyzer also uses

simulation, user mode, and default toggle rate assignments to determine power

consumption. Altera strongly recommends using the PowerPlay Power Analyzer

when your FPGA design is complete.

f

For more information about how to use the PowerPlay Power Analyzer in the

Quartus II software, refer to the

chapter in volume 3 of the

Quartus II Handbook.

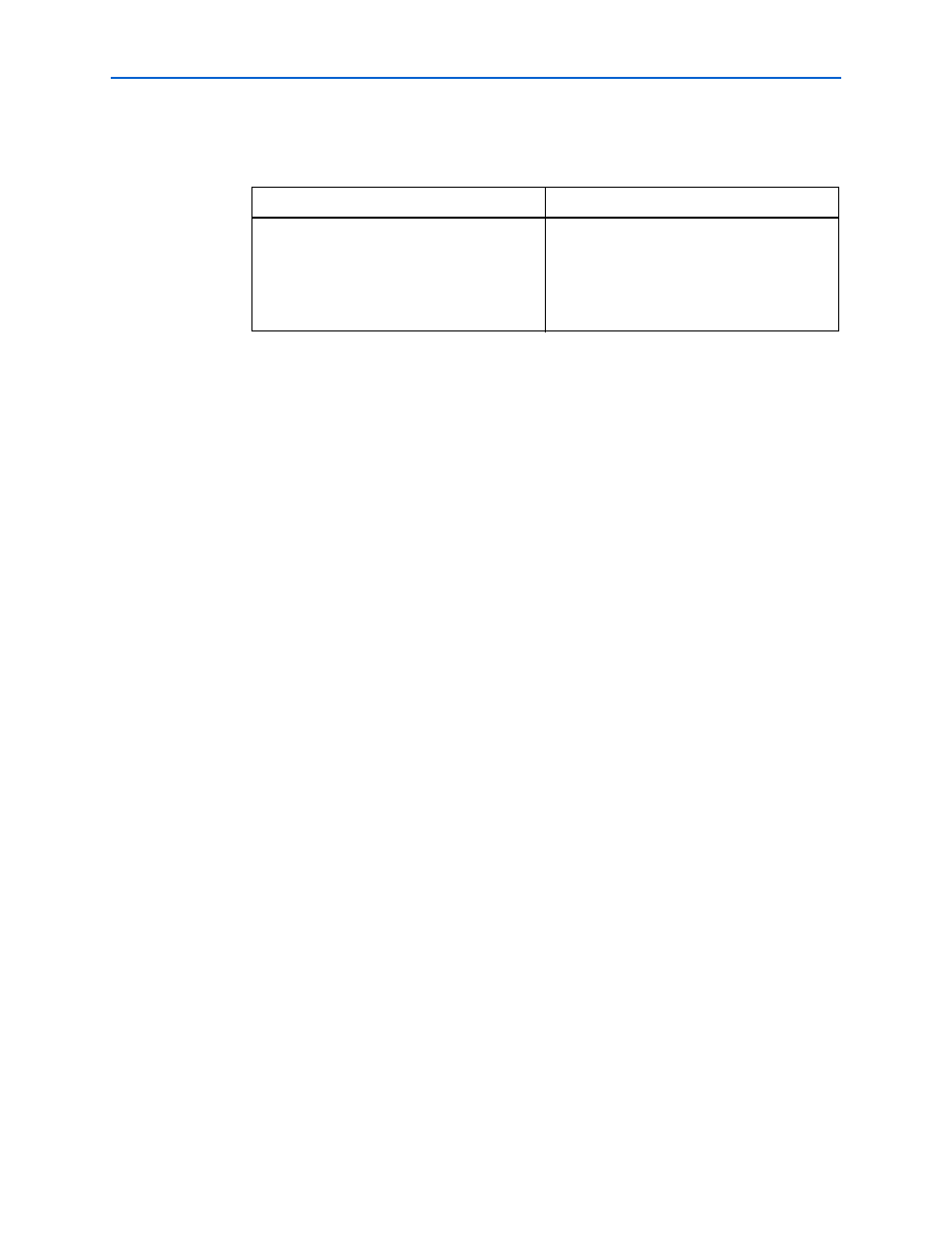

Table 2–2. Power Estimation When FPGA Design Is Partially Complete

Advantages

Disadvantages

■

Power estimation can be done early in the

FPGA design cycle.

■

Provides the flexibility to automatically fill in

the PowerPlay Early Power Estimator based

on Quartus II software compilation results.

■

Accuracy dependents on your input and

estimate of the final design device

resources—this information can change

during or after the completion of your design,

therefore affecting the accuracy of your

power estimation results.