Altera Arria II GX FPGA Development Board, 6G Edition User Manual

Page 45

Chapter 2: Board Components

2–37

Components and Interfaces

© July 2010 Altera Corporation

Arria II GX FPGA Development Board, 6G Edition Reference Manual

J1.102

Dedicated CMOS I/O bit 41

HSMB_D41

LVDS or 2.5-V

AL2

J1.103

Dedicated CMOS I/O bit 42

HSMB_D42

AK3

J1.104

Dedicated CMOS I/O bit 43

HSMB_D43

AL1

J1.107

Dedicated CMOS I/O bit 44

HSMB_D44

AJ4

J1.108

Dedicated CMOS I/O bit 45

HSMB_D45

AK1

J1.109

Dedicated CMOS I/O bit 46

HSMB_D46

AJ3

J1.110

Dedicated CMOS I/O bit 47

HSMB_D47

AJ1

J1.113

Dedicated CMOS I/O bit 48

HSMB_D48

AJ2

J1.114

Dedicated CMOS I/O bit 49

HSMB_D49

AH3

J1.115

Dedicated CMOS I/O bit 50

HSMB_D50

AH6

J1.116

Dedicated CMOS I/O bit 51

HSMB_D51

2.5-V

AH4

J1.119

Dedicated CMOS I/O bit 52

HSMB_D52

AC10

J1.120

Dedicated CMOS I/O bit 53

HSMB_D53

M10

J1.121

Dedicated CMOS I/O bit 54

HSMB_D54

AC11

J1.122

Dedicated CMOS I/O bit 55

HSMB_D55

M9

J1.125

Dedicated CMOS I/O bit 56

HSMB_D56

M8

J1.126

Dedicated CMOS I/O bit 57

HSMB_D57

L7

J1.127

Dedicated CMOS I/O bit 58

HSMB_D58

M7

J1.128

Dedicated CMOS I/O bit 59

HSMB_D59

K8

J1.131

Dedicated CMOS I/O bit 60

HSMB_D60

K7

J1.132

Dedicated CMOS I/O bit 61

HSMB_D61

J8

J1.133

Dedicated CMOS I/O bit 62

HSMB_D62

K6

J1.134

Dedicated CMOS I/O bit 63

HSMB_D63

J6

J1.137

Dedicated CMOS I/O bit 64

HSMB_D64

J7

J1.138

Dedicated CMOS I/O bit 65

HSMB_D65

G5

J1.139

Dedicated CMOS I/O bit 66

HSMB_D66

H7

J1.140

Dedicated CMOS I/O bit 67

HSMB_D67

F5

J1.143

Dedicated CMOS I/O bit 68

HSMB_D68

G6

J1.144

Dedicated CMOS I/O bit 69

HSMB_D69

D5

J1.145

Dedicated CMOS I/O bit 70

HSMB_D70

G4

J1.146

Dedicated CMOS I/O bit 71

HSMB_D71

C6

J1.149

Dedicated CMOS I/O bit 72

HSMB_D72

D6

J1.150

Dedicated CMOS I/O bit 73

HSMB_D73

C5

J1.151

—

—

—

J1.152

—

—

—

J1.155

LVDS or CMOS clock out 2 or CMOS bit 76

HSMB_CLKOUT_P2

N8

J1.156

Dedicated CMOS I/O bit 74

HSMB_D74

AE5

J1.157

LVDS or CMOS clock out 2 or CMOS bit 77

HSMB_CLKOUT_N2

N7

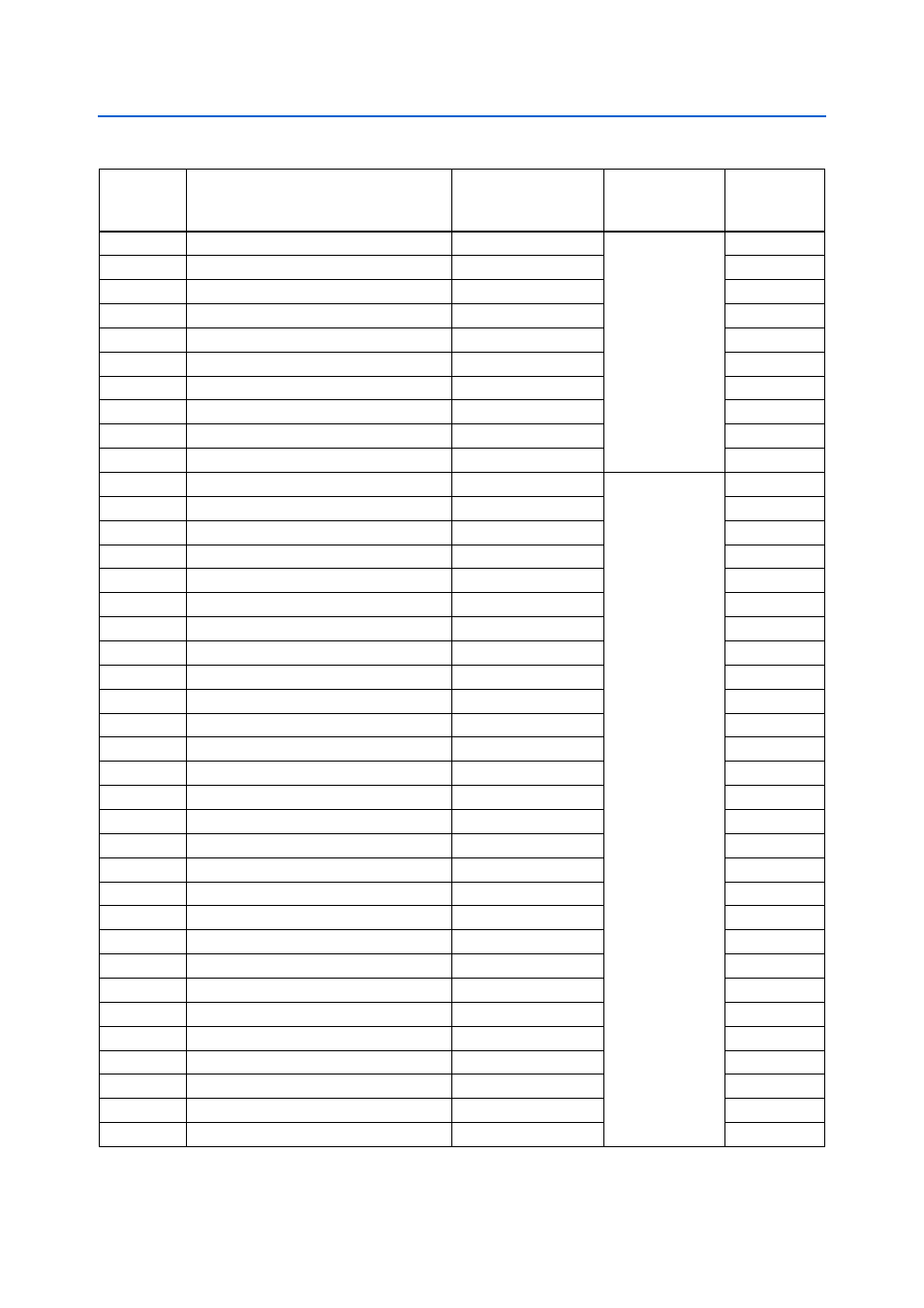

Table 2–37. HSMC Port B Pin Assignments, Schematic Signal Names, and Functions (Part 3 of 4)

Board

Reference

Description

Schematic Signal

Name

I/O Standard

Arria II GX

Device

Pin Number