Altera Stratix II EP2S180 DSP Development Board User Manual

Page 19

Altera Corporation

Core Version a.b.c variable

2–11

Stratix II EP2S180 DSP Development Board Reference Manual

Board Components & Interfaces

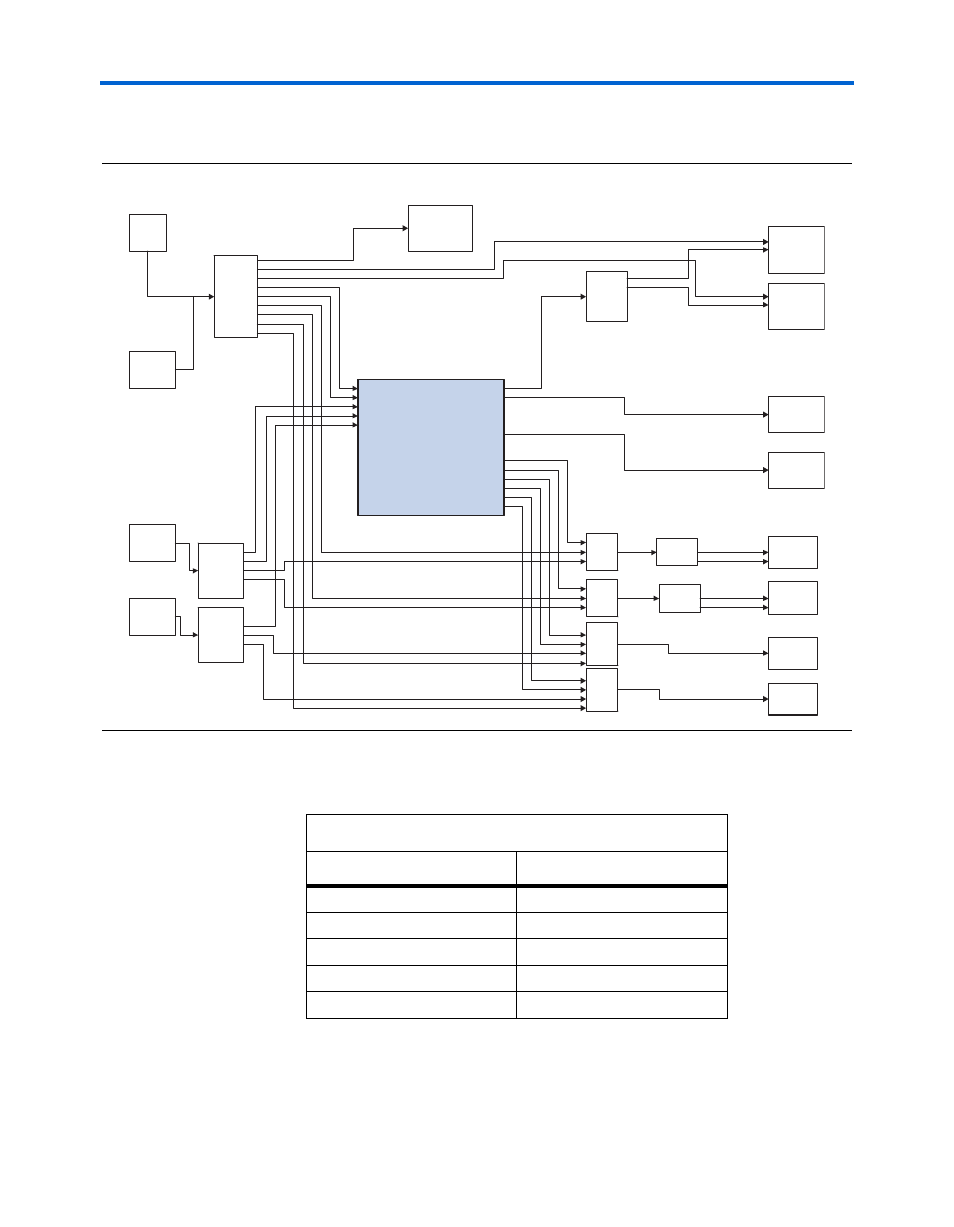

shows each clock and its distribution throughout the board.

Figure 2–3. Clock Distribution

lists reference information for the 100-MHz socketed oscillator.

100-MHz

Oscillator

Clock

Distribution

2

CLK_IN_p

CLK_IN_n

DA_EXT_CLK

Expansion

Prototype

Connector

CLK

Buffer

CLK

Buffer

ADC A

ADC B

DAC

DAC

Configuration

Controller

SDRAM

Audio

CODEC

ADC A

Jumper

ADC B

Jumper

DAC A

Jumper

DAC B

Jumper

Clock

Distribution

4

Clock

Distribution

3

Clock

Distribution

1

Expansion

Prototype

Connector

Stratix II

EP2S180F1020C3

Device

Table 2–5. 100-MHz Socketed Oscillator Reference

Item

Description

Board reference

Y1

Part number

ECS-UPO-8PIN 100MHz

Device description

Oscillator

Manufacturer

ECS Inc.

Manufacturer web site

www.ecsxtal.com