Electrical specifications, Advisory note for electrical specifications, Equalization and pre-emphasis – Altera SerialLite II Protocol User Manual

Page 14

14

Altera Corporation

SerialLite II Protocol Reference Manual

Physical Layer Description

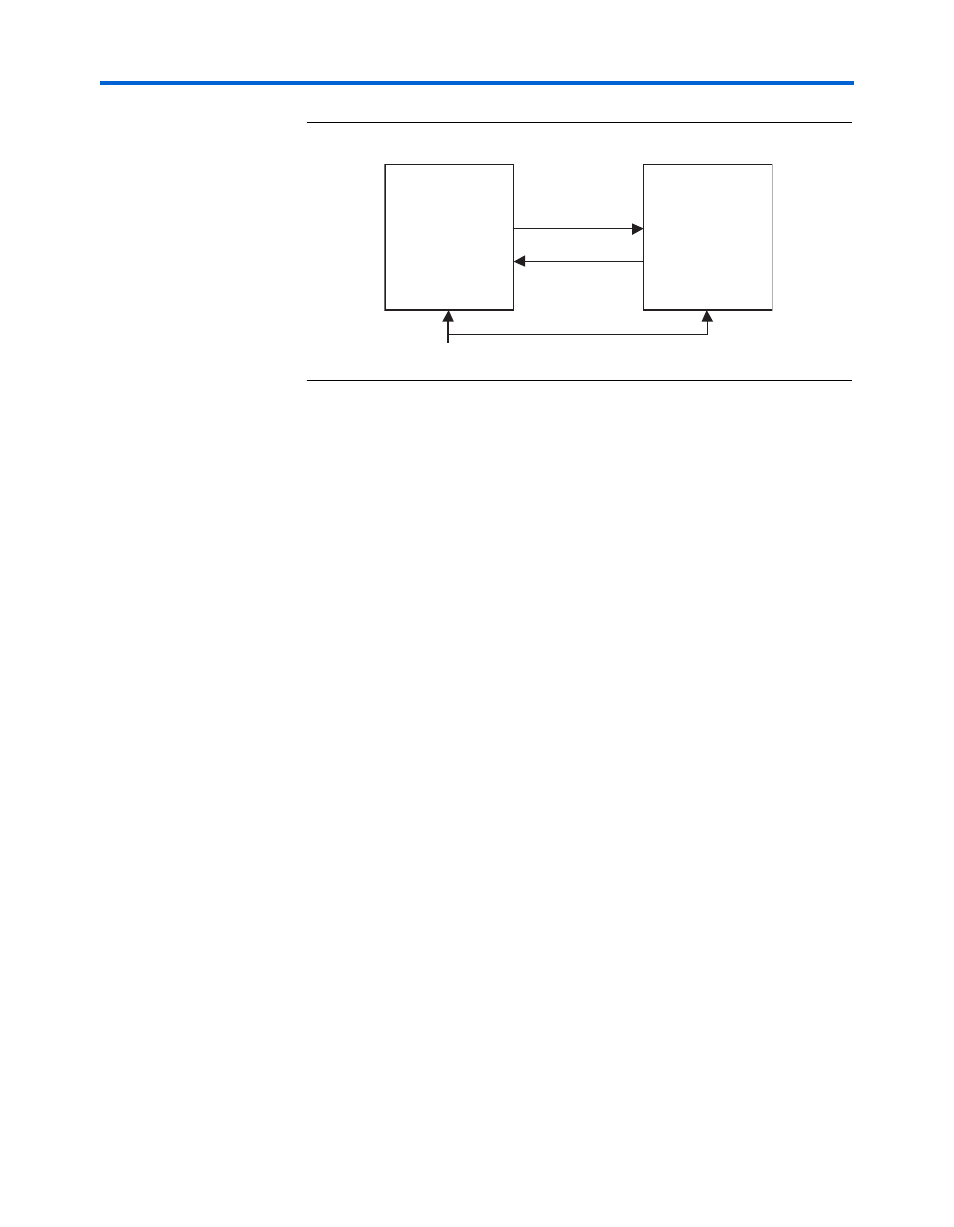

Figure 2–5. Synchronous Clock & Data Recovery

Electrical Specifications

This section defines the electrical specifications for the SerialLite II

Physical layer. The AC electrical specifications are given for the

transmitter and receiver, and cover single- and multi-lane instantiations.

To ensure interoperability between components operating from different

supply voltages or implemented in different technologies, use AC

coupling at the receiver input.

Advisory Note for Electrical Specifications

The parameters for the AC electrical specifications are based on existing

electrical interfaces. For example, SerialLite II can use the XAUI electrical

interface specified in Clause 47 of IEEE 802.3ae-2002, or the CEI electrical

interface specified in Clause 6 of OIF-CEI-02.0. This standard usage

allows electrical designs for SerialLite II to reuse electrical designs from

the XAUI and CEI, suitably modified for applications at the

SerialLite II-specific baud interval and reach described in this

specification.

Where elements of the electrical specification follow the exact XAUI

specification, this document points to the XAUI and CEI documents.

Where there are differences motivated by the frequency range supported

by SerialLite II, the applicable SerialLite II information is provided.

Equalization and Pre-emphasis

The use of high-speed serial links causes the interconnect media to

degrade the signal at the receiver, which produces effects such as

inter-symbol interference (ISI) or data-dependent jitter. The signal loss

Device A

Device B

TD[0-N]

RD[0-N]

RD[0-N]

TD[0-N]

REFCLK