Link deskew ordered set sequence {|tds, Clock compensation ordered set sequence ({|cc|}), Link initialization and training – Altera SerialLite II Protocol User Manual

Page 27

Altera Corporation

27

SerialLite II Protocol Reference Manual

SerialLite II Specification

Link Deskew Ordered Set Sequence {|TDS|}

This sequence is used in the lane bonding process to allow alignment of

all lanes in a multi-lane link.

Clock Compensation Ordered Set Sequence ({|CC|})

The clock compensation sequence is used by the clock compensation

circuitry to adapt between two clocks having slightly different

frequencies within a specified tolerance. See

for a detailed description.

Link Initialization and Training

Link initialization and training is the process of preparing the link for its

normal operation of transferring data. Single and duplex links have

different state machines. For a duplex link, acknowledgement from the

TSZ

||DAT||

Transfer size. Valid numbers are 1, 2, and

4. The transfer size defines the number of

columns for a contiguous burst of data; 1

column, 2 columns, 4 columns, and all

other values are reserved.

RSV

3x||DAT||

Reserved. Set to all zeros (D0.0) repeated

three times

T2

||DAT||

Second training sequence identifier (D5.2)

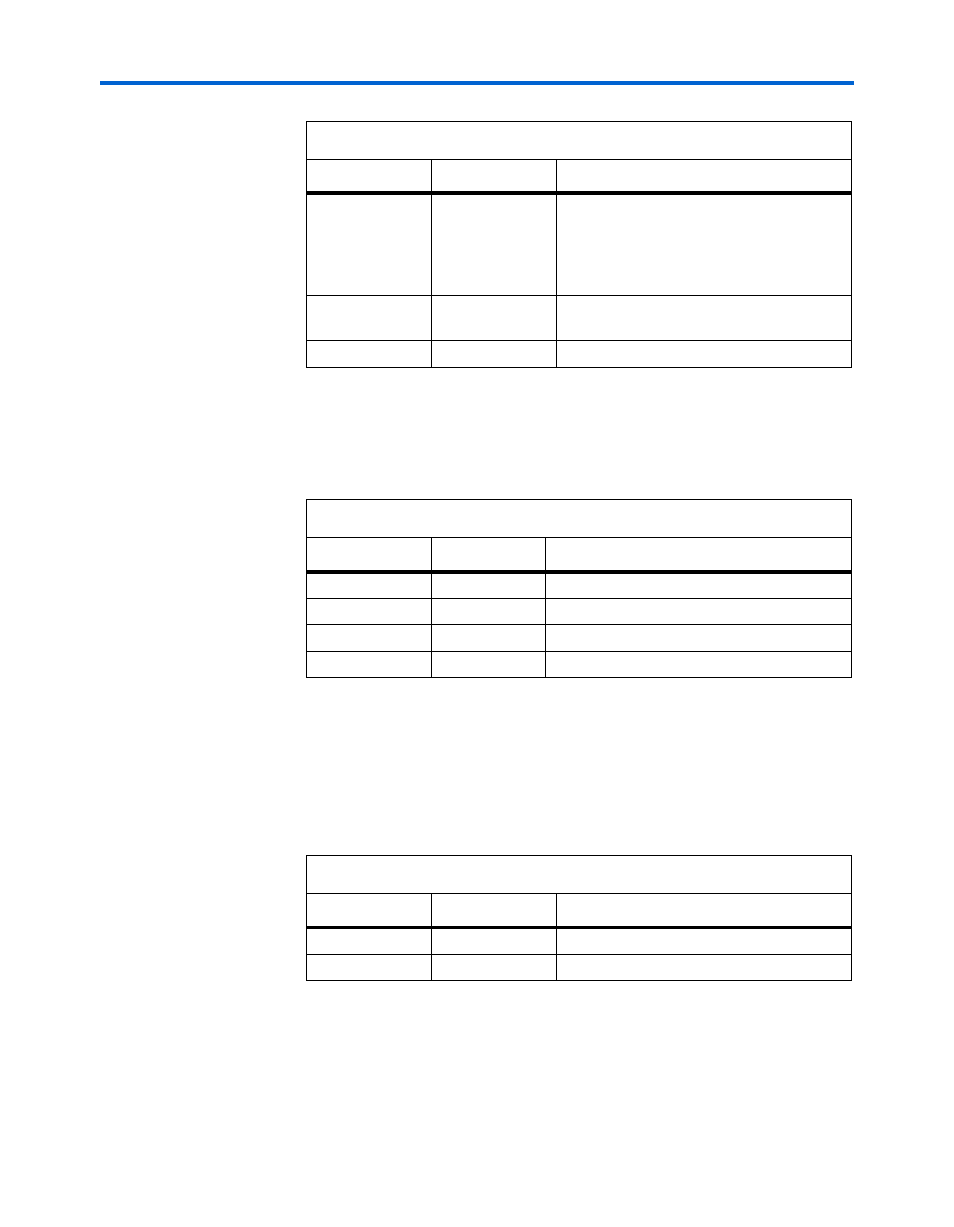

Table 2–15. {|TDS|} Composition

Field

Ordered Set

Description

TDS1

4x {|TS2|}

{|TS2|} Order sequence repeated four times

TDS2

||COM||

Comma (or Sync) identifier

TDS3

||ALN||

Align identifier

TDS4

2x ||IDL||

Idle identifier repeated twice

Table 2–16. {|CC|} Composition

Field

Ordered Set

Description

CC1

||COM||

Comma (or Sync) identifier

CC2

3x ||IDL||

Idle (Skip) identifier repeated three times

Table 2–14. {|TS2|} Composition

Field

Ordered Set

Description