Scrambling (optional), Rules for scrambling – Altera SerialLite II Protocol User Manual

Page 35

Altera Corporation

35

SerialLite II Protocol Reference Manual

SerialLite II Specification

1.

All lanes must have the same frequency.

2.

The receiver removes any {|CC|} sequence.

3.

The transmitter must send one clock compensation sequence

({|CC|}) at each scheduled interval.

4.

The transmitter must schedule insertion at least once every 1,666

columns in case of +/- 300 ppm, or at least once every 5,000 columns

in case of +/- 100 ppm.

5.

The transmitter must insert a clock compensation sequence into all

lanes simultaneously.

6.

The clock compensation sequence has the highest transmission

priority and can interrupt any transmission. It is inserted

irrespective of whether a frame is in transmission or is an idle

period.

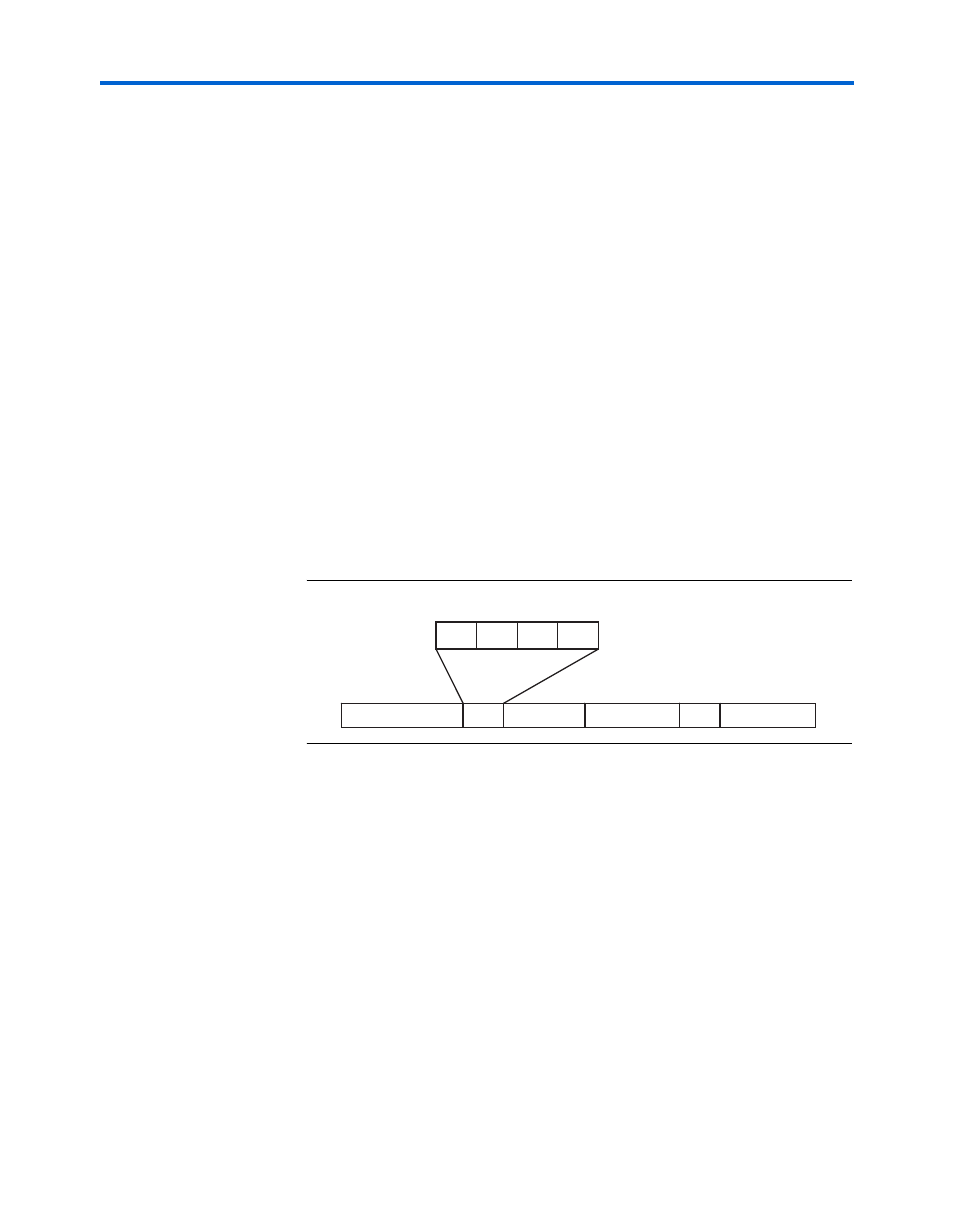

shows an example of the clock tolerance compensation

sequence insertion.

Figure 2–15. Clock Tolerance Compensation Insertion Example

Scrambling (Optional)

Scrambling can reduce EMI by eliminating repeating characters, which

has a great effect at high data rates. A linear feedback shift register (LSFR)

is used as a pseudo-random number generator to scramble the data,

using the G(x) = X16 + X5 + X4 + X3 + 1 polynomial.

The transmitted bits are XORed with the output of the LFSR in the data

stream. At the receiver, the data stream is again XORed with an identical

scrambler to recover the original bits. To synchronize the transmitter to

the receiver, the COM character initializes the LFSR with the initial seed

of 'hFFFF XORed with the lane number (LN).

Rules for Scrambling

The following scrambling rules must be followed:

Data Packet

CC

Data Packet

Priority Packet

Idle

Data Packet

COM

IDL

IDL

IDL