Altera Hybrid Memory Cube Controller User Manual

Page 13

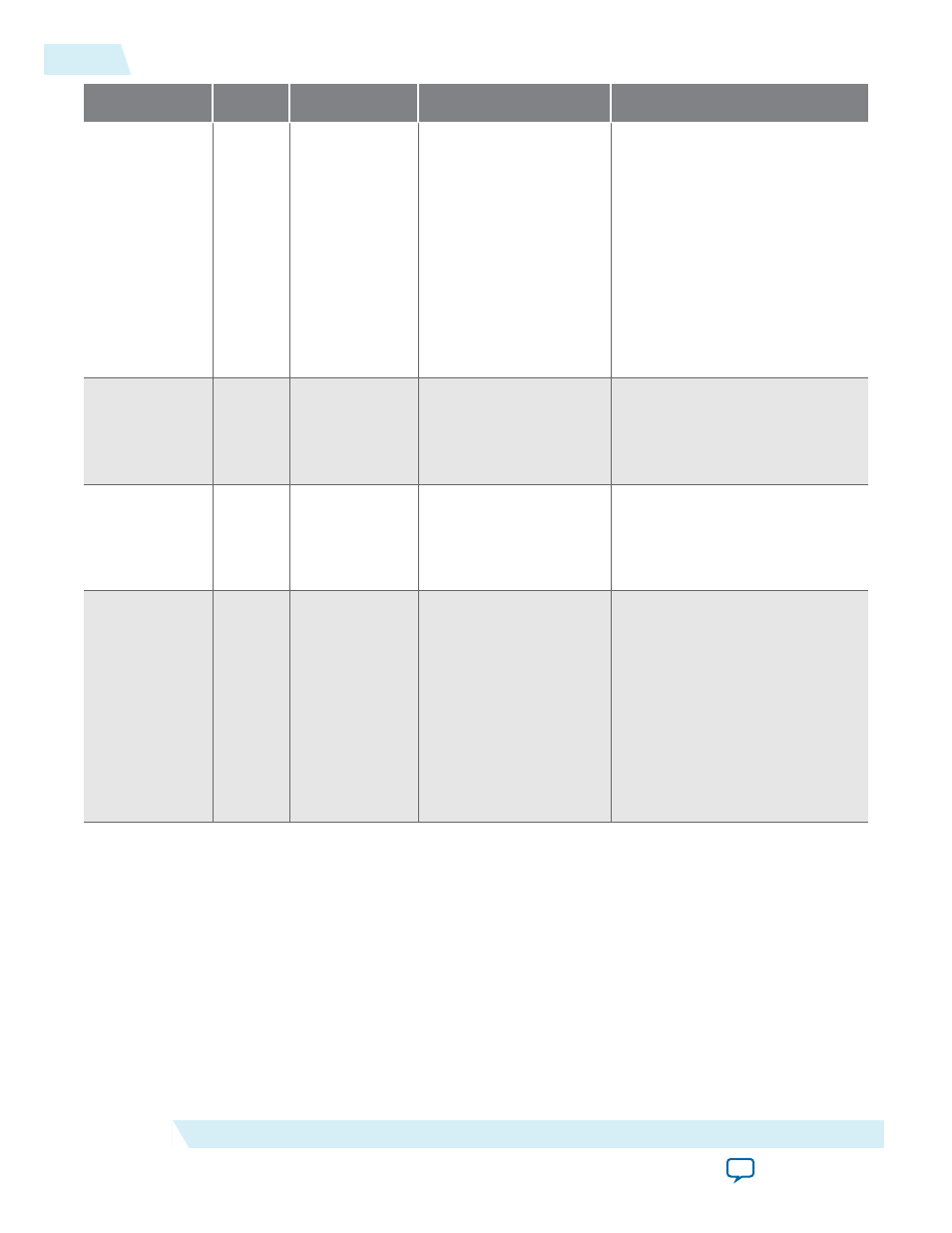

Parameter

Type

Range

Default Setting

Parameter Description

CDR

reference

clock

String

• 312.5 MHz

(at 10 Gbps

only)

• 390.625 MHz

(at 12.5 Gbps

only)

• 125 MHz

• 156.25 MHz

• 166.67 MHz

125 MHz

Selects the input reference clock

for the RX CDR PLL. You must

drive the

rx_cdr_refclk0

input

signal at the frequency you

specify for this parameter.

In addition, your design must

derive this clock, the external

transceiver TX PLL reference

clock, and the

REFCLKP

and

REFCLKN

input signals of the

external HMC device from the

same clock source.

RX mapping 64-bit

value

0xFEDCBA9876543210

Selects the RX lane mapping.

Use caution in modifying this

parameter. Refer to RX and TX

Mapping Parameters.

TX mapping 64-bit

value

0xFEDCBA9876543210

Selects the TX lane mapping.

Use caution in modifying this

parameter. Refer to RX and TX

Mapping Parameters.

Enable

Altera

Debug

Master

Endpoint

(ADME)

Boolean • True

• False

False

Specifies whether the IP core

turns on the ADME feature in

the embedded Arria 10 Native

PHY IP core that configures the

transceivers.

The ADME feature enables

Native PHY register program‐

ming with the Altera System

Console. For more information,

refer to the Arria 10 Transceiver

PHY User Guide.

2-4

HMC Controller IP Core Parameters

UG-01152

2015.05.04

Altera Corporation

Getting Started with the HMC Controller IP Core