Status and debug signals, Status and debug signals -11 – Altera Hybrid Memory Cube Controller User Manual

Page 48

Related Information

•

Control and Status Register Interface

on page 3-3

•

HMC Controller IP Core Register Map

•

Describes the

INTERRUPT_STATUS

,

INTERRUPT_ENABLE

, and

INTERRUPT_GLOBAL_ENABLE

registers.

•

For more information about the Avalon-MM protocol, including timing diagrams, refer to the Avalon

Memory-Mapped Interfaces chapter.

Status and Debug Signals

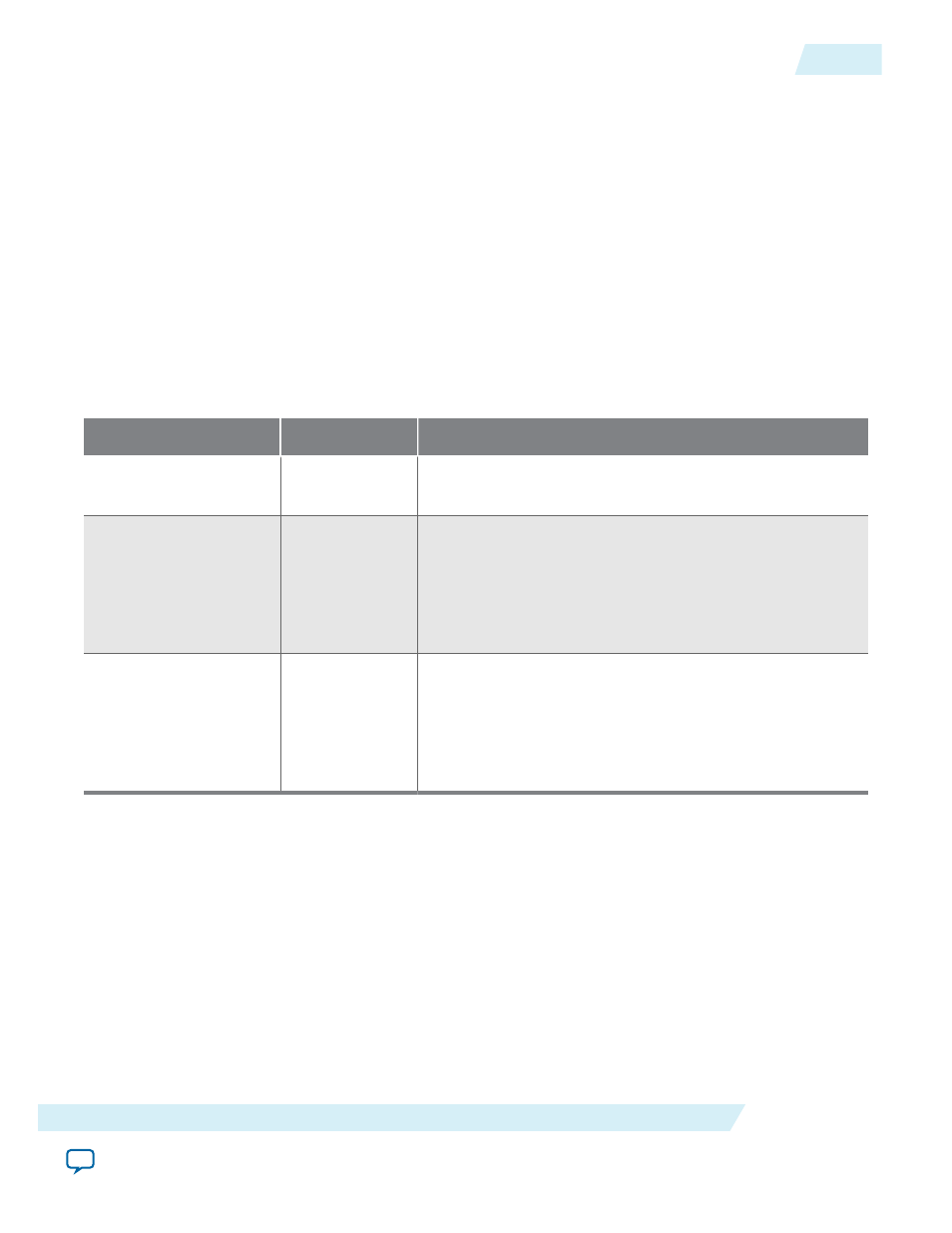

Table 4-6: Status and Debug Signals

The HMC Controller IP core status and debug interface provides a few extra signals to communicate successful

link initalization and to support debugging of your HMC system.

Clock Name

Direction

Description

link_init_complete

Output

The IP core asserts this signal when the link initialization

state machine is in the active state.

debug_tx_

data[511:0]

(for full-

width IP cores)

debug_tx_

data[255:0]

(for half-

width IP cores)

Output

This data bus shows an unscrambled copy of the striped data

before it enters the TX lane swapper. The data on this bus is

striped but not scrambled.

debug_rx_

data[511:0]

(for full-

width IP cores)

debug_rx_

data[255:0]

(for half-

width IP cores)

Output

This data bus shows the striped and descrambled received

data after processing by the RX lane swapper and the

descrambler.

Related Information

on page 3-3

UG-01152

2015.05.04

Status and Debug Signals

4-11

HMC Controller IP Core Signals

Altera Corporation