Altera Hybrid Memory Cube Controller User Manual

Page 58

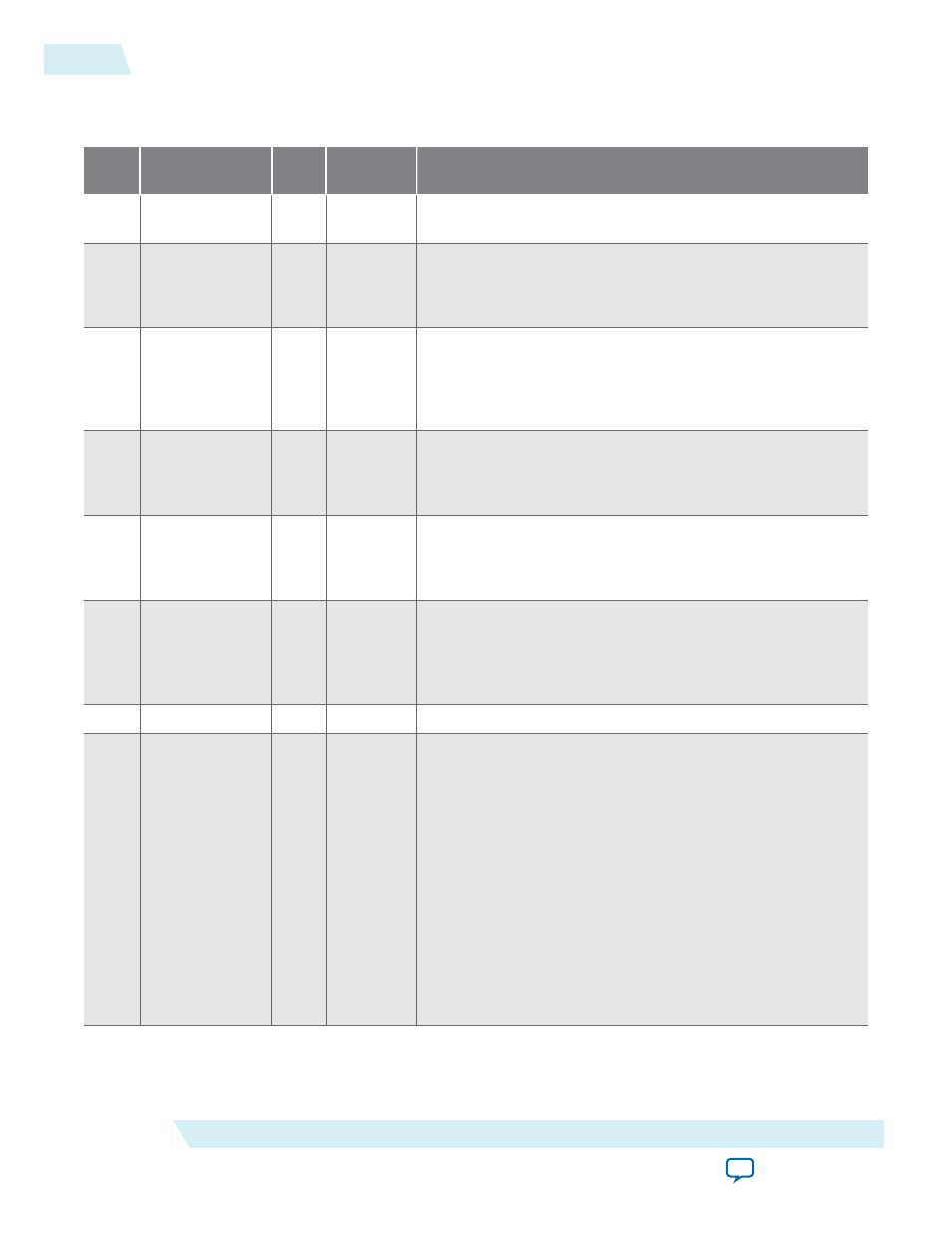

Table 5-8: HMC Controller IP Core INTERRUPT_STATUS Register at Offset 0x20

To clear an interrupt, write the value of 1 to the interrupt bit.

Bits

Field Name

Type

Value on

Reset

Description

31:

16

Reserved

RO

0x0000

15

Response Queue

Uncorrectable

ECC Error

W1C 0x0

The IP core sets this bit if it detects an uncorrectable ECC

error in the Response Queue memory. The IP core can

detect such an error only if you turn on Enable M20K ECC

support in the parameter editor.

14

Response Queue

ECC Error

W1C 0x0

The IP core sets this bit if it detects a correctable ECC error

in the Response Queue memory. If the IP core sets this bit it

also corrects the ECC error. The IP core can detect such an

error only if you turn on Enable M20K ECC support in the

parameter editor.

13

FERR_N

W1C 0x0

The IP core sets this bit if the HMC device indicates a fatal

error by asserting its active-low FERR_N pin. You must

connect the IP core

hmc_ferr_n

input signal to the HMC

device

FERR_N

output signal.

12

Retry Buffer

Uncorrectable

ECC Error

W1C 0x0

The IP core sets this interrupt bit if it detects an uncorrect‐

able ECC error in the Retry Buffer memory. The IP core can

detect such an error only if you turn on Enable M20K ECC

support in the parameter editor.

11

Retry Buffer

ECC Error

W1C 0x0

The IP core sets this interrupt bit if it detects a correctable

ECC error in the Retry Buffer memory. The IP core

automatically corrects the ECC in this case. The IP core can

detect such an error only if you turn on Enable M20K ECC

support in the parameter editor.

10 Reserved

RO

0x0

9

No More Tokens

W1C 0x0

The IP core sets this interrupt bit if it runs out of tokens.

Tokens represent available buffer space in the HMC device.

While the IP core has no remaining tokens, it does not send

any additional requests, per token-based flow control

requirements. This situation is not an error condition, but it

may indicate a reduction in performance. However, like any

interrupt bit, it causes the IP core to assert the

csr_irq

signal (assuming the global interrupt enable register bit is

set).

This bit has the value of 0 when the IP core comes out of

reset. After link initialization, the HMC device communi‐

cates its buffer capacity with a sequence of TRET packets.

After the IP core receives the first TRET packet, it begins

updating the

No More Tokens

register field.

5-6

Interrupt Related Registers

UG-01152

2015.05.04

Altera Corporation

HMC Controller IP Core Register Map