Link_status register, Link_status register -4 – Altera Hybrid Memory Cube Controller User Manual

Page 56

Bits

Field Name

Type

Value on

Reset

Description

7:0

(half-

width IP

core)

DescramSync

RO

0x00

Each bit indicates whether the descrambler for the

corresponding transceiver channel has synchron‐

ized to the received data.

15:0

(full-

width IP

core)

DescramSync

RO

0x0000

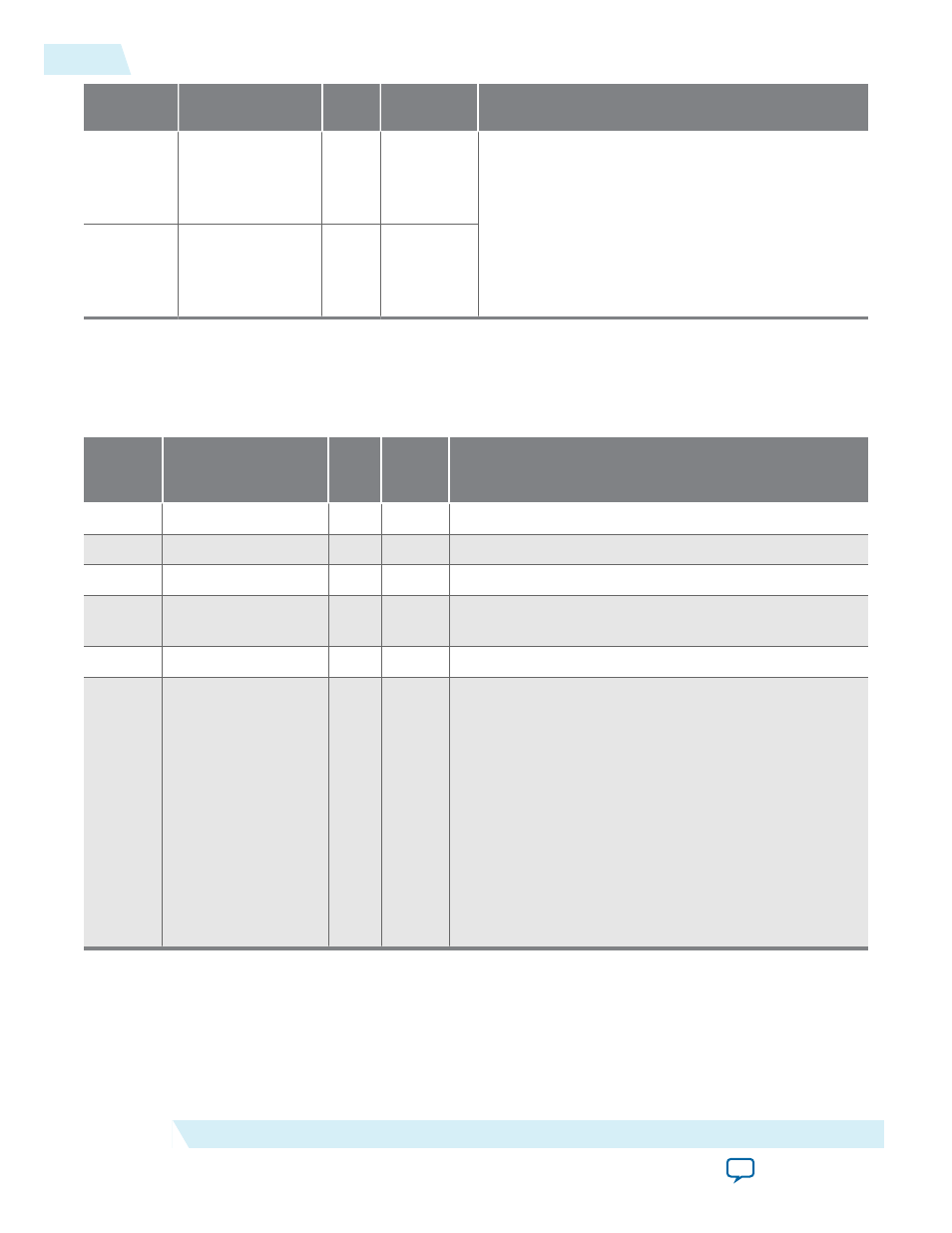

LINK_STATUS Register

Table 5-6: HMC Controller IP Core LINK_STATUS Register at Offset 0x10

Bits

Field Name

Type

Value

on

Reset

Description

31:17 Reserved

RO

0x0000

16

RXPS

RO

0x0

Level of the LxRXPS input from the HMC device.

15:9

Reserved

RO

0x00

8

LanesAligned

RO

0x0

Indicates whether the received data is aligned across all

lanes.

7:6

Reserved

RO

0x0

5:0

InitializationStat

e

RO

0x01

Indicates the current state in link initialization. This

register field has the following valid values:

• 6'b100000: Active

• 6'b010000: Transaction Initialization (Wait for

TRET)

• 6'b001000: Word Synchronization (Transmit TS1)

• 6'b000100: Scrambler Synchronization (Transmit

NULLs)

• 6'b000010: HMC Configuration (by the external I

2

C

master module)

• 6'b000001: Reset

Related Information

on page 3-5

Describes the behavior of the

InitializationState

field during HMC Controller IP core initialization.

5-4

LINK_STATUS Register

UG-01152

2015.05.04

Altera Corporation

HMC Controller IP Core Register Map