Altera Active Serial Memory Interface User Manual

Page 14

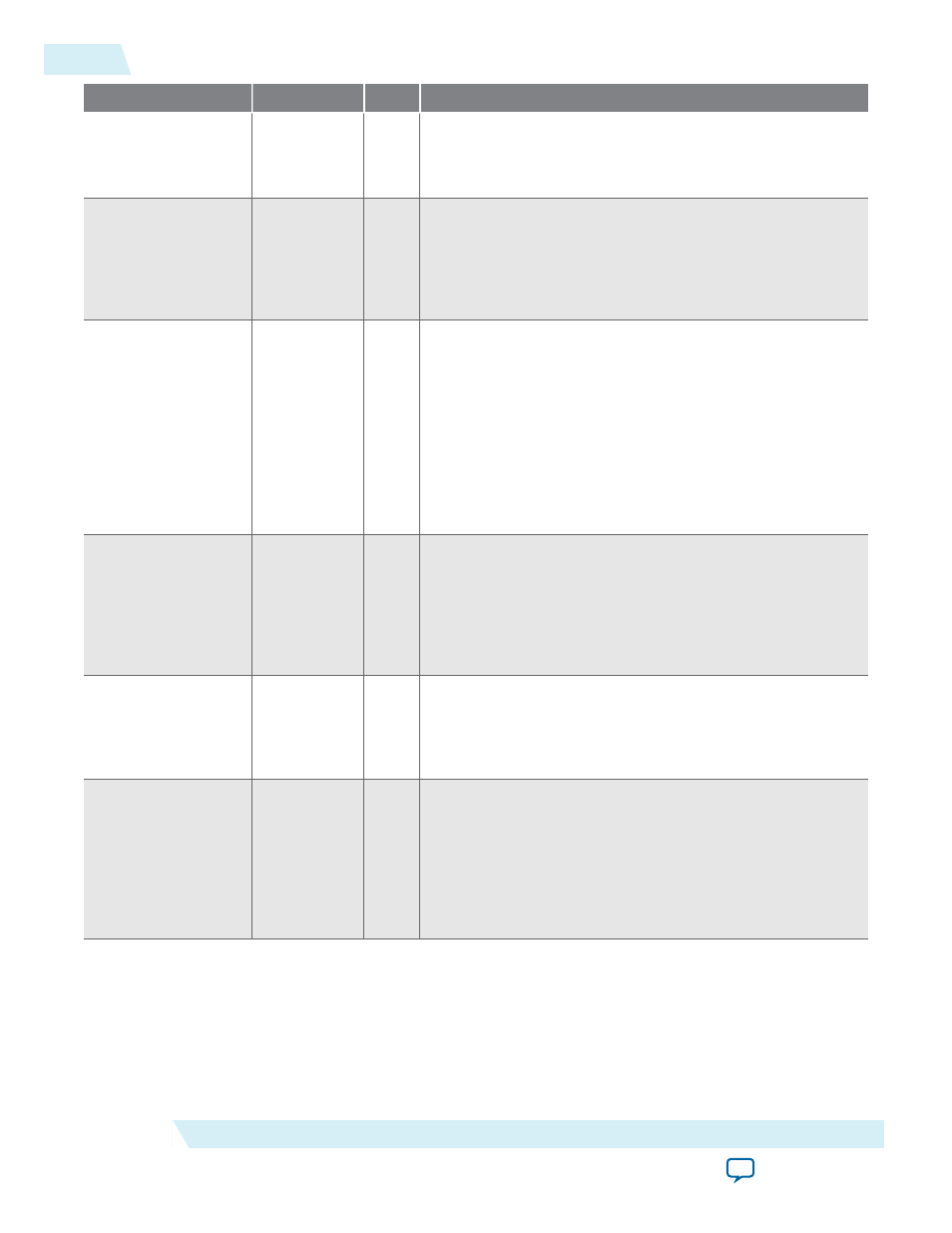

Port

Condition

Size

Descriptions

read_sid

Optional

1 bit Active-high port that executes the read silicon ID operation.

If asserted, the IP core proceeds to read the silicon ID of the

EPCS device, and the value of the silicon ID appears at the

epcs_id[7..0]

port.

read_status

Optional

1 bit Active-high port that executes the read EPCS/EPCQ/EPCQ-

L status register operation. If asserted, the IP core reads the

status register of the EPCS/EPCQ/EPCQ-L device, and

outputs the value at the

status_out[7..0]

port. You can

use the

read_status

port to determine which memory

sector on the EPCS/EPCQ/EPCQ-L device is read-only.

reset

Required

1 bit To reset all counters and registers in the Altera ASMI

Parallel IP core (not the EPCS/EPCQ/EPCQ-L devices), pull

the

reset

signal high for at least two clock cycles.

The

reset

signal is asserted regardless of busy status, hence,

do not assert the

reset

signal whenever the Altera ASMI

Parallel IP core is running.

After asserting the

reset

signal, allow two clock cycles to

reset the circuit before sending a new signal.

Default value of the reset port is 0.

sector_erase

Optional

1 bit Active-high port that executes the sector erase operation. If

asserted, the IP core starts erasing the memory sector on the

EPCS/EPCQ/EPCQ-L device based on the memory address

value at the

addr[23..0]

port. The value is a valid memory

address in the sector to be erased. For EPCQ256/EPCQ-

L256 or larger devices, the width of the

addr

and

read_

address

signals is 32 bit.

sector_protect

Optional

1 bit Active-high port that executes the sector protect operation.

If asserted, the IP core takes the value of the

datain[7..0]

port and writes to the EPCS/EPCQ/EPCQ-L status register.

The status register contains the block protection bits that

represent the memory sector to be protected.

shift_bytes

Optional

1 bit Active-high port that shifts data bytes during the write

operation. You must use this port together with the write

port during the page-write operation. The IP core samples

and shifts the data in the

datain[7..0]

port at the rising

edge of the

clkin

signal, as long as the

shift_bytes

signal

is asserted. Continue shifting the required bytes into the

EPCS/EPCQ/EPCQ-L device until the IP core finishes

sampling and storing the data internally.

14

Input Ports

UG-ALT1005

2014.12.15

Altera Corporation

Altera ASMI Parallel IP Core User Guide