Altera Active Serial Memory Interface User Manual

Page 24

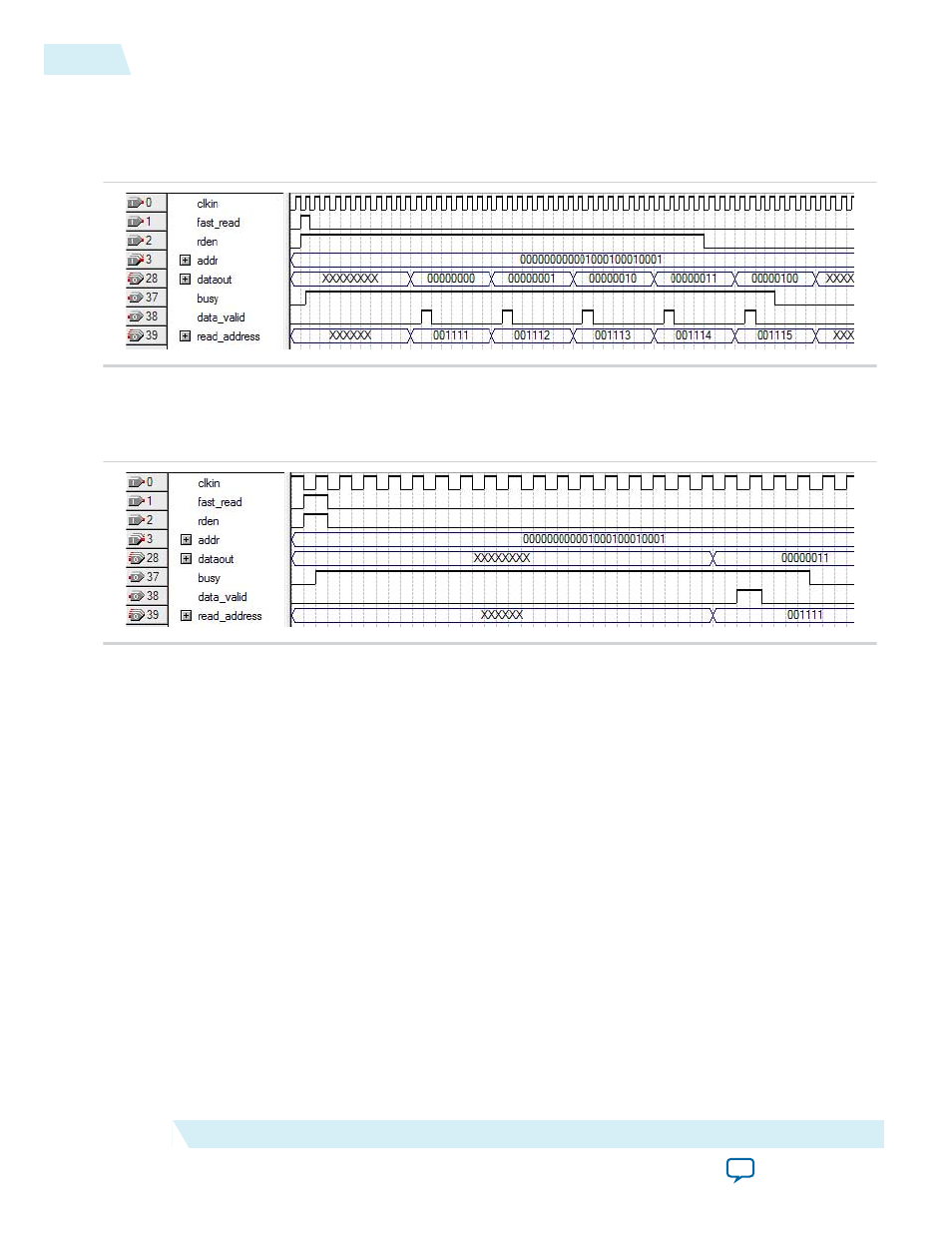

Figure 8: Fast Reading Multiple-Byte

This figure shows an example of the latency when the Altera ASMI Parallel IP core is executing multiple-

byte fast read command. The latency shown does not correctly indicate the true processing time. The

latency only shows the command.

Figure 9: Fast Reading a Single-Byte

This figure shows an example of single-byte read command. The latency shown does not correctly

indicate the true processing time. The latency only shows the command.

The fast read command is the same as the read command, with the following exceptions:

• The fast read command produces the first byte of data on the

dataout[7..0]

port eight cycles

later than it appears for the read command.

• The fast read command is available for all EPCS/EPCQ/EPCQ-L devices, except for EPCS1

and EPCS4 devices.

• The fast read command can run up to 25 MHz clock frequency.

• The fast read and the read commands are mutually exclusive—you can use only one of them in

each IP core instantiation.

• The fast read and read operations are mutually exclusive. You can only do either read or fast

read operation at a time. The fast read operation is a replacement for the read operation at

higher than 20 MHz clock frequency.

The IP core registers the

fast_read

signal on the rising edge of the

clkin

signal. For the IP core

to register the read command, ensure that the memory address appears on the

addr[23..0]

signal before the

fast_read

signal is asserted. The

rden

signal must also be asserted to enable the

fast read command.

After the IP core registers the

fast_read

signal, the

busy

signal is asserted to indicate that the fast

read command is in progress. The data appears on the

dataout[7..0]

signal. The first valid byte

of fast read data appears eight clock cycles later than it appears in a normal read command. Also,

after the first byte, subsequent bytes appear sequentially, similar to any multiple-byte normal read

24

Fast Read Data from the EPCS/EPCQ/EPCQ-L Device

UG-ALT1005

2014.12.15

Altera Corporation

Altera ASMI Parallel IP Core User Guide