Altera Active Serial Memory Interface User Manual

Page 5

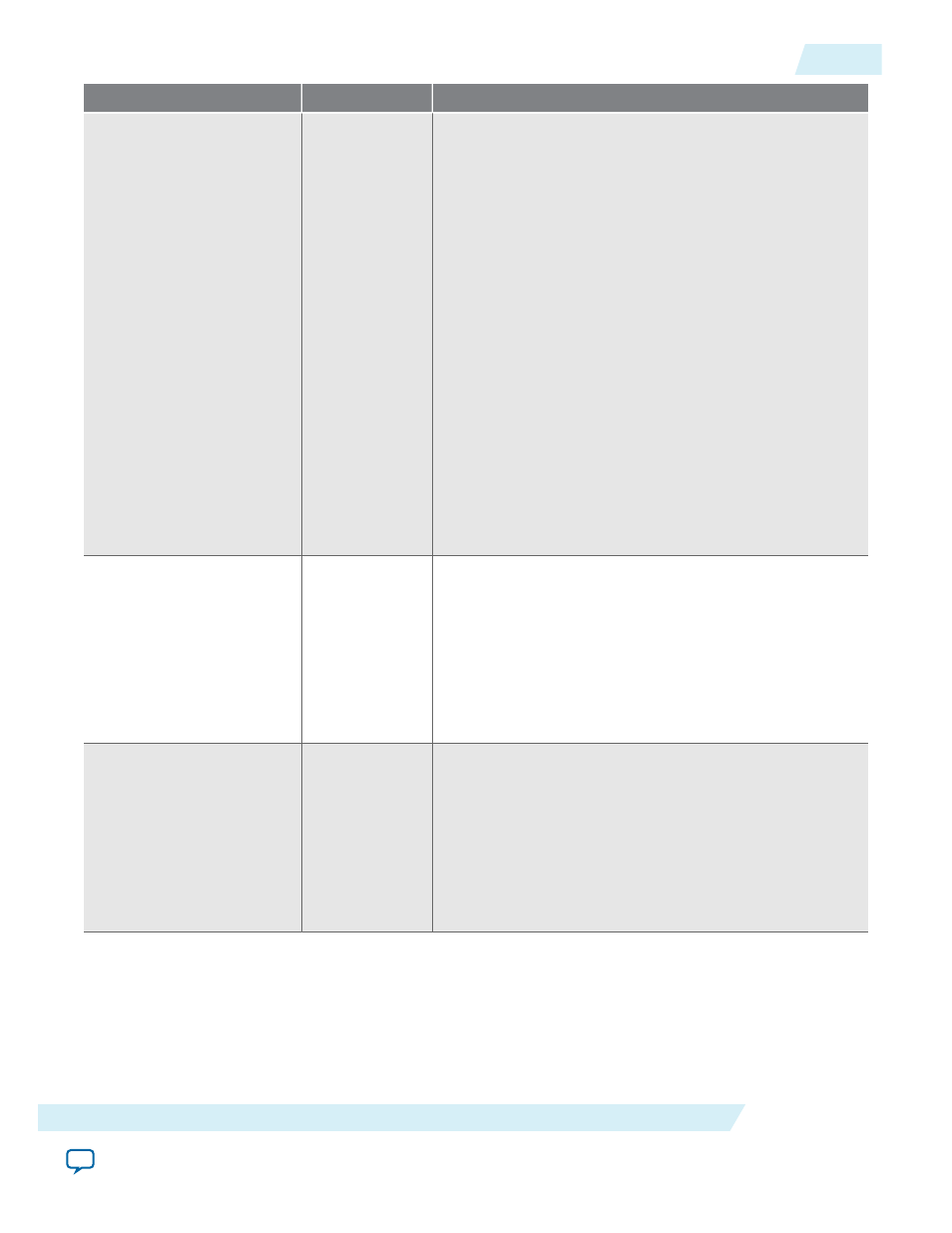

Parameter

Legal Values

Descriptions

Configuration device

type

EPCS1,

EPCS4,

EPCS16,

EPCS64,

EPCS128,

EPCQ16,

EPCQ32,

EPCQ64,

EPCQ128,

EPCQ256,

EPCQ512,

EPCQ-L256,

EPCQ-L512,

EPCQ-L1024

• Specify the EPCS/EPCQ/EPCQ-L type you want to use.

• The default value is EPCS4.

Use ‘read_sid’ port

—

• Enables the ability to read the silicon ID of the EPCS

device with an active-high

read_sid

input signal.

When this signal is asserted, the IP core reads the

silicon ID of the EPCS device. After reading the silicon

ID, the 8-bit silicon ID appears on the

epcs_

id[7..0]

signal until the device resets.

• This option is available only for EPCS1, EPCS4,

EPCS16, and EPCS64 devices.

Use ‘read_status’ port

—

• Enables the ability to read the port status using an

active-high input signal named

read_status

. When

this signal is asserted, the IP core reads the EPCS/

EPCQ/EPCQ-L status register. As the status register is

read, the 8-bit value appears on the

status_

out[7..0]

signal.

• This option is available for all EPCS/EPCQ/EPCQ-L

devices.

UG-ALT1005

2014.12.15

Parameters

5

Altera ASMI Parallel IP Core User Guide

Altera Corporation