Altera Active Serial Memory Interface User Manual

Page 28

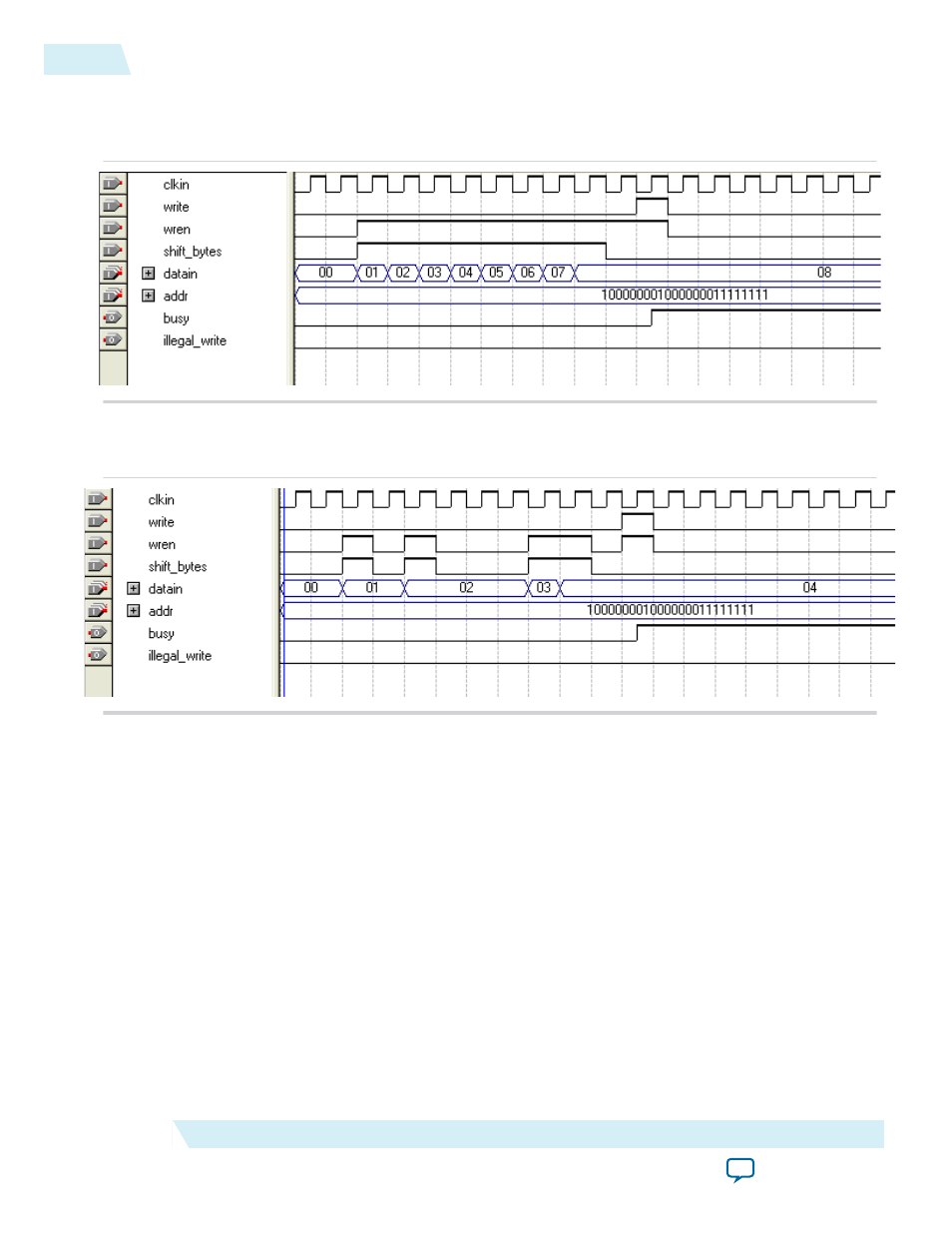

Figure 12: Page-Write Operation: Example 1

This figure shows an example of the page-write operation when the

PAGE_SIZE

parameter has a value of

eight.

Figure 13: Page-Write Operation: Example 2

This figure shows an example of writing four bytes of data.

The IP core executes the page-write sequence in two stages: stage 1 and stage 2.

For stage 1, you must assert the

wren

and

shift_bytes

signals to enable the IP core to sample the

data byte at

datain[7..0]

signal and to store the byte internally in the page-write buffer. The IP

core samples

datain[7..0]

signal at the rising edge of the

clkin

signal.

You do not need to ensure that a new data byte is available with each clock cycle; however, you

can use the

shift_bytes

signal to control when the IP core takes in a new data byte. Every time a

new data byte is ready at

datain[7..0]

signal, assert the

shift_bytes

signal for one clock cycle

to enable the IP core to sample the data. Set the

wren

signal to a value of one.

Continue controlling the

shift_bytes

and

wren

signals until the entire data bytes shift into the

page-write buffer for writing.

You can write any number of data bytes less than the

PAGE_SIZE

parameter value set in the IP

parameter editor.

Note: If you send more data bytes than the

PAGE_SIZE

parameter value, the IP core

writes only the last (equivalent to

PAGE_SIZE

value) number of bytes to the EPCS/

28

Page-Write Operation

UG-ALT1005

2014.12.15

Altera Corporation

Altera ASMI Parallel IP Core User Guide