Altera Active Serial Memory Interface User Manual

Page 17

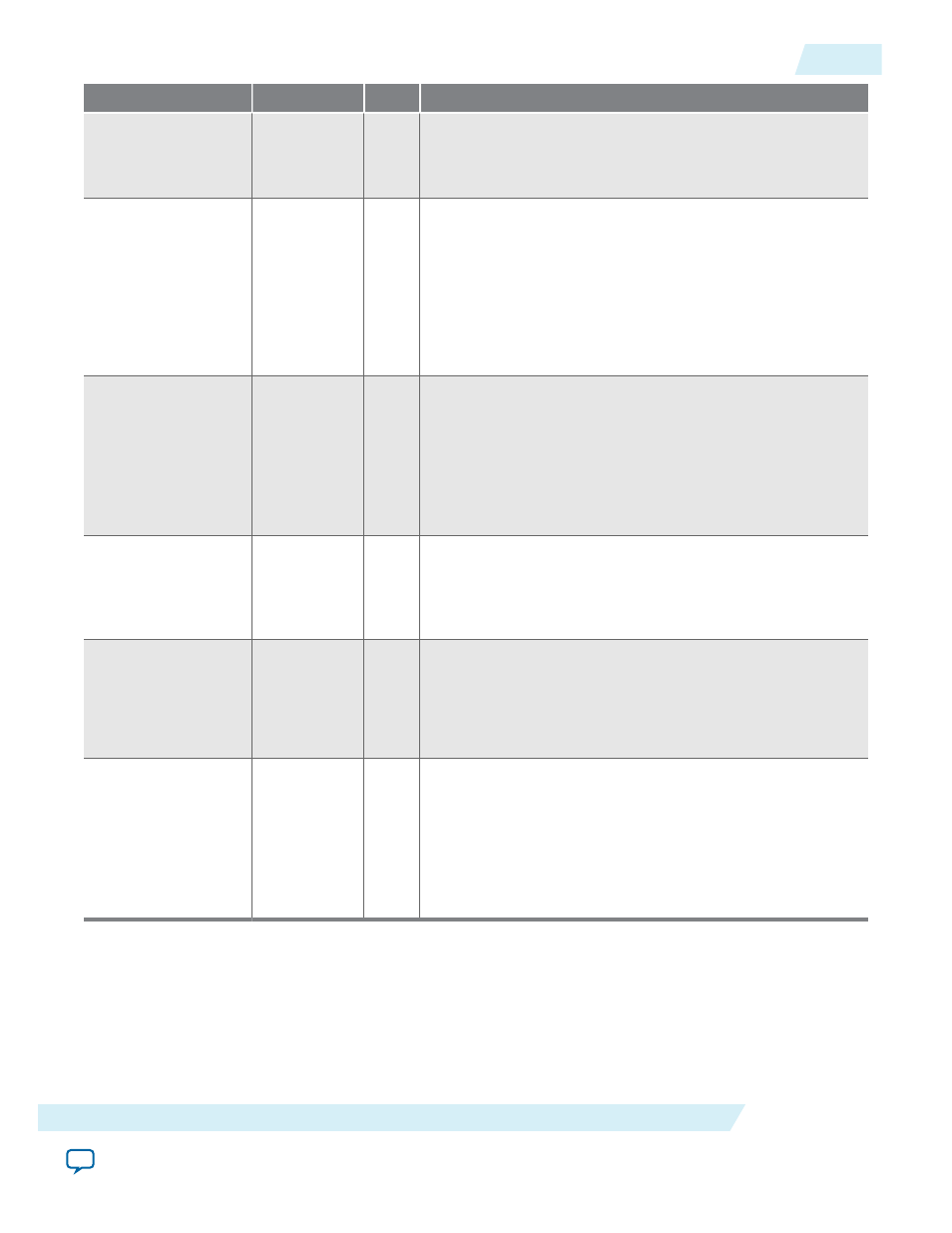

Port

Condition

Size

Descriptions

epcs_id[]

Optional

8 bit Contains the silicon ID of the EPCS device after the read

silicon ID operation. This port holds the value of the silicon

ID until the device resets. Sample the

epcs_id[7..0]

port

after the

busy

signal goes low.

illegal_erase

Optional

1 bit Indicates that an erase instruction has been set to a

protected sector on the EPCS/EPCQ/EPCQ-L memory. This

port is required when you specify the

sector_erase

port,

bulk_erase

port, or

die_erase

port. The

illegal_erase

signal goes high to indicate that the IP core has cancelled the

erase instruction. The signal pulses high for two clock cycles

—one clock cycle before, and one clock cycle after the

busy

signal goes low. Monitor this port to detect the status of an

erase operation.

illegal_write

Optional

1 bit Indicates that a write instruction is targeting a protected

sector on the EPCS/EPCQ/EPCQ-L memory. This port is

required when you specify the write port. The

illegal_

write

signal goes high to indicate that the IP core has

cancelled a write instruction. The signal pulses high for two

clock cycles—one clock cycle before, and one clock cycle

after the

busy

signal goes low. Monitor this port to detect

the status of a write operation.

rdid_out[]

Optional

8 bit Contains the memory capacity ID of the EPCS/EPCQ/

EPCQ-L device after the read memory capacity ID

operation is completed. This port holds the value until the

device resets. Sample the

rdid_out[7..0]

port after the

busy

signal goes low.

read_address[]

Optional

24 or

32 bit

Contains the memory address of the EPCS/EPCQ/EPCQ-L

to be read from. Use this port together with the

dataout[7..0]

port.

For EPCQ256/EPCQ-L256 or larger devices, the width of

the

addr

and

read_address

signals is 32 bit.

status_out[]

Optional

8 bit Contains the value of the EPCS/EPCQ/EPCQ-L status

register after the read status register operation is completed.

This port holds the value until you execute another reading

status register operation, or until you reset the device. To

obtain the most recent value of the status register, you must

perform a read status register operation before sampling the

status_out[7..0]

port. Sample the port only after the

busy

signal goes low.

Related Information

• on page 26

For more information about the write operation

• on page 23

For more information about the read operation

• on page 20

For more information about the read silicon ID operation

UG-ALT1005

2014.12.15

Output Ports

17

Altera ASMI Parallel IP Core User Guide

Altera Corporation