Output ports – Altera Active Serial Memory Interface User Manual

Page 16

• on page 21

For more information about the sector protect operation

• on page 26

For more information about the write operation

• on page 26

For more information about the write operation

Output Ports

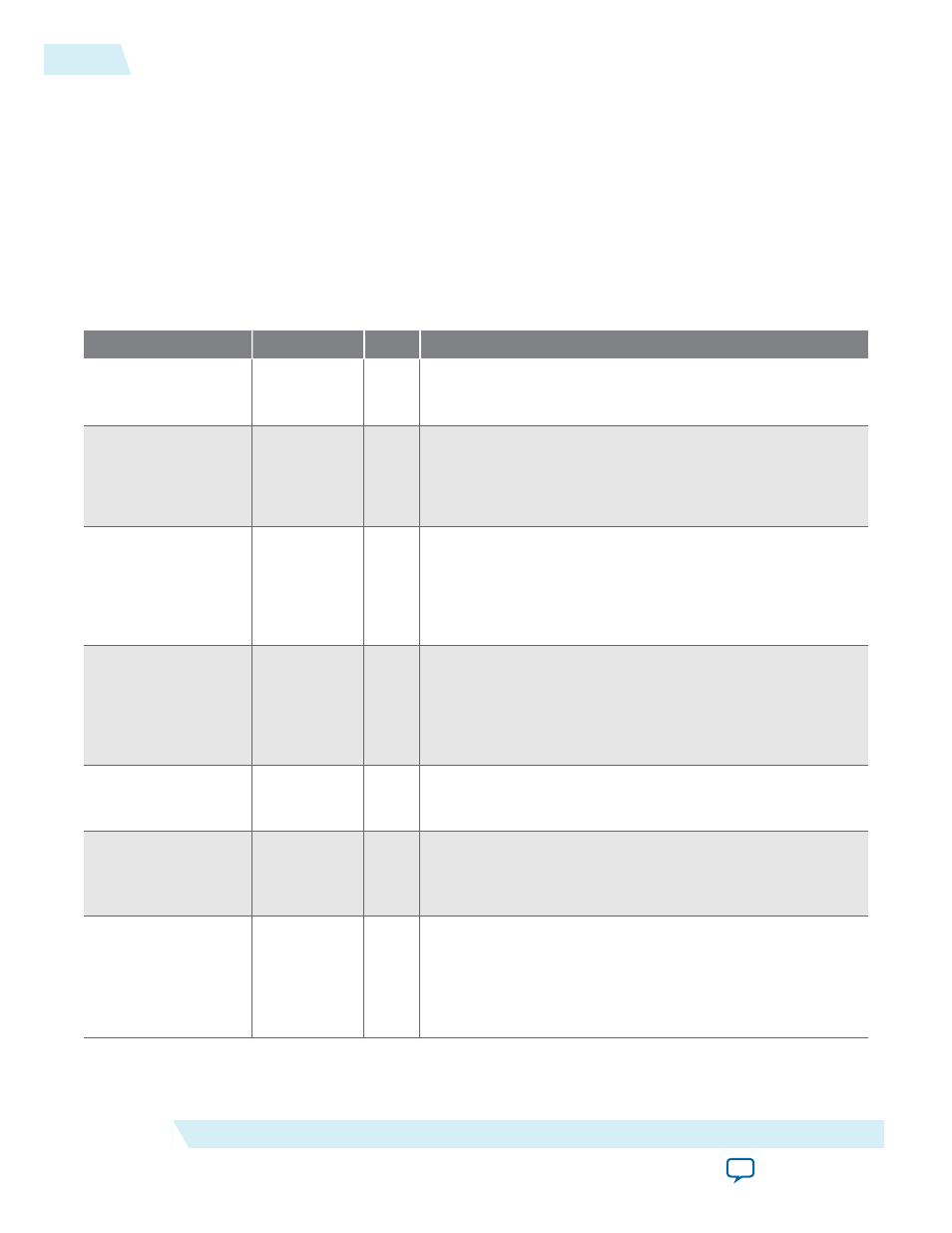

This table lists the output ports for the Altera ASMI Parallel IP core.

Table 3: Output Ports

Port

Condition

Size

Descriptions

asmi_dclk

Optional

1 bit Provides clock signal to the EPCS/EPCQ/EPCQ-L device

when you select the Disable dedicated Active Serial

interface option.

asmi_scein

Optional

1 or 3

bit

Provides the

ncs

signal to the EPCS/EPCQ/EPCQ-L device

when you select the Disable dedicated Active Serial

interface option.

If you are using Arria 10 devices, the bit size is 3.

asmi_sdoin

Optional

1 or 4

bit

Provides data signal to the EPCS/EPCQ/EPCQ-L device

when you select the Disable dedicated Active Serial

interface option.

If you are using Arria V, Cyclone V, Stratix V, or Arria 10

devices, then the bit size is 4.

asmi_dataoe

Optional

1 or 4

bit

Provides data input/output control signal to the EPCS/

EPCQ/EPCQ-L device when you the Disable dedicated

Active Serial interface option.

If you are using Arria V, Cyclone V, Stratix V, or Arria 10

devices, then the bit size is 4.

busy

Required

1 bit Indicates the IP core is performing a valid operation. The

busy

signal goes high when the IP core is executing a valid

operation, and goes low after the operation.

data_valid

Required

1 bit Indicates that the

dataout[7..0]

port contains a valid data

byte read from the EPCS/EPCQ/EPCQ-L memory. Sample

the

dataout[7..0]

port only when the

data_valid

signal is

high.

dataout[]

Required

8 bit Contains the data byte read from the EPCS/EPCQ/EPCQ-L

memory during read operation. This port holds the value of

the last data byte read until the device resets, or until the IP

core carries out a new read operation. Sample the

dataout[7..0]

port only when the

data_valid

signal is

high.

16

Output Ports

UG-ALT1005

2014.12.15

Altera Corporation

Altera ASMI Parallel IP Core User Guide