Altera QDRII SRAM Controller MegaCore Function User Manual

Page 44

3–12

MegaCore Version 9.1

Altera Corporation

QDRII SRAM Controller MegaCore Function User Guide

November 2009

Interfaces & Signals

shows a burst of two, the controller takes the data straight

away and puts it on the QDRII SRAM interface a few cycle later (the exact

timing may change). Because it takes as many Avalon clock cycles as

QDRII SRAM clock cycles to write the data, you can put write accesses

back-to-back. The write cycles have no influence on the read cycles as the

address is put on half a clock cycle.

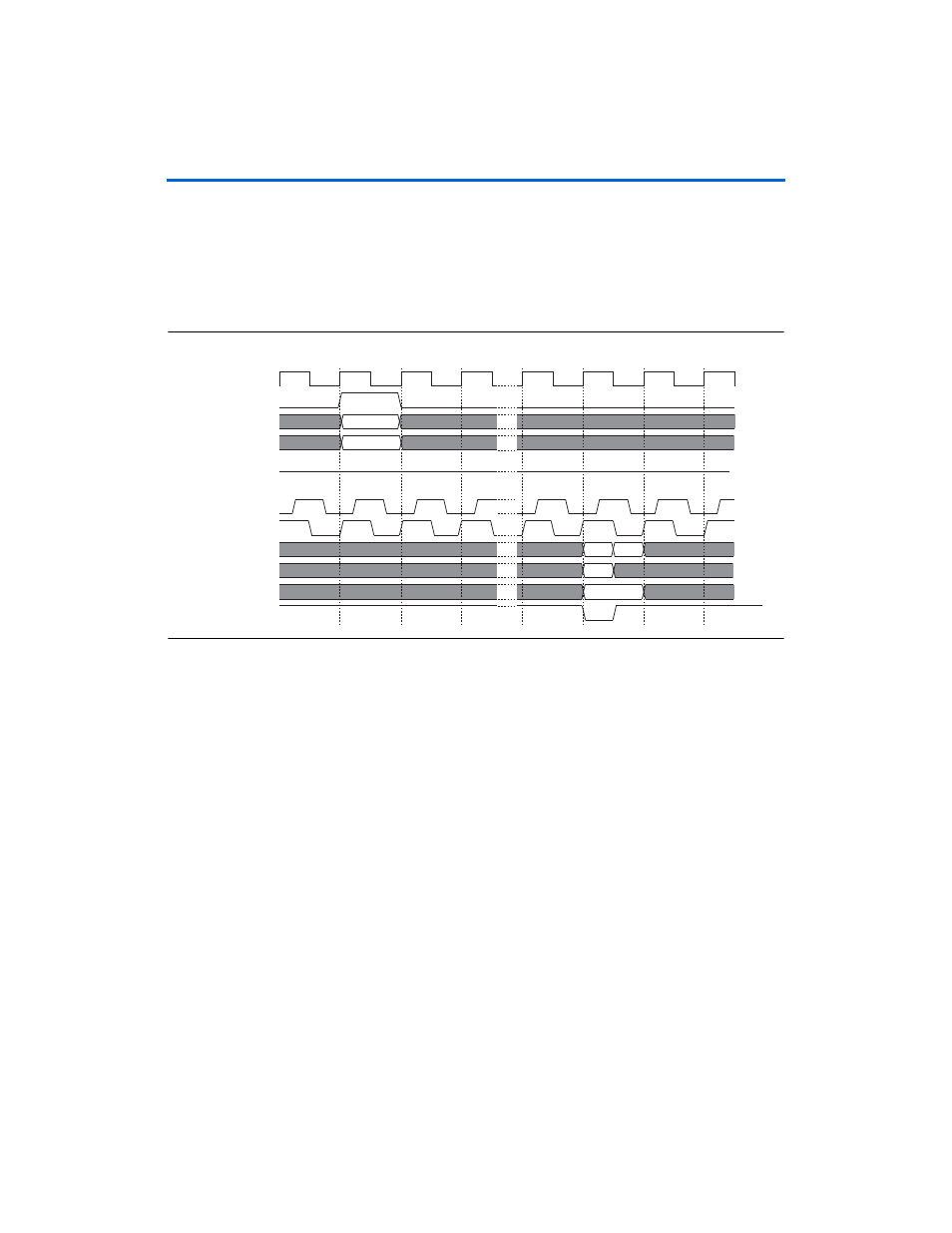

Figure 3–8. Write—Burst of Two

shows a burst of four (wide mode), all the data is

present in one clock cycle. After one Avalon write, you can transfer data

for two clock cycles on the QDRII SRAM interface. In this example, all the

data bits are valid and the byte mask is set to enable the whole transfer.

avl_write

avl_data_wr[35:0]

avl_adr_wr[19:0]

avl_wait_request_wr

system_cl k

qdrii_d[17:0]

qdrii_a[19:0]

qdrii_bwsn[1:0]

qdrii_wpsn

00010002

00010002

0001

0001

0001 0002

0002

0001

0001

00

00

avl_clk

avl_clock_wr