Signals – Altera QDRII SRAM Controller MegaCore Function User Manual

Page 54

3–22

MegaCore Version 9.1

Altera Corporation

QDRII SRAM Controller MegaCore Function User Guide

November 2009

Interfaces & Signals

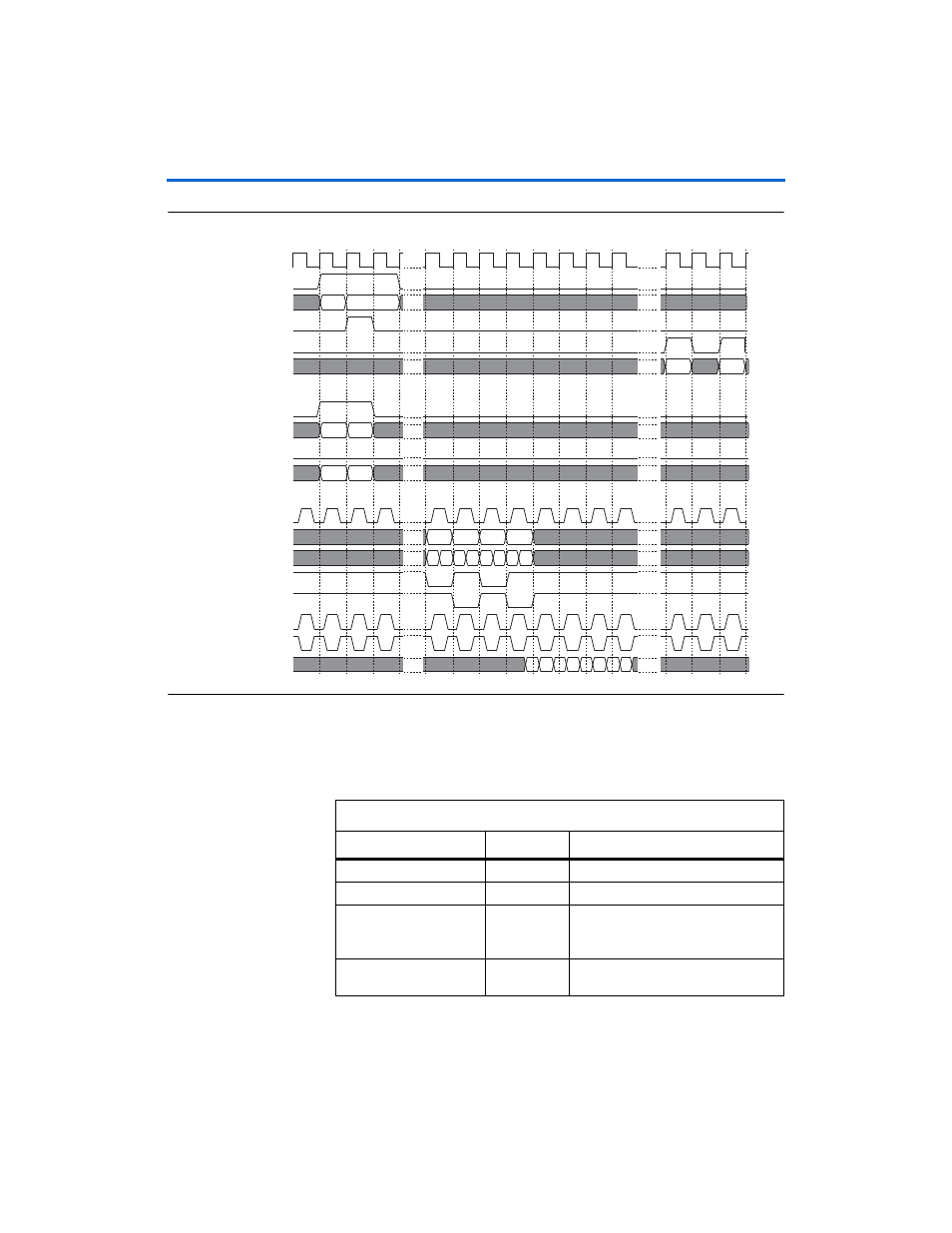

Figure 3–19. Simultaneous Read & Write—Burst of Four (Wide Mode)

Signals

shows the system signals.

avl_clk

avl_read

avl_adr_rd[19:0]

avl_wait_request_rd

avl_data_read_valid

avl_data_rd[17:0]

avl_write

avl_adr_wr[19:0]

avl_wait_request_wr

avl_data_wr[17:0]

qdrii_k

qdrii_a[19:0]

qdrii_d[17:0]

qdrii_wpsn

qdrii_rpsn

qdrii_cqn

qdrii_cq

qdrii_q[17:0]

51

52

52

9abc

dfe0

dfe0

01

02

02

1234 5678

5678

51

01

52

02

02

1 2 3 4 5 6 7 8

8

9 a b c d e

f

0

0

Table 3–1. System Signals (Part 1 of 2)

Signal

Direction

Description

avl_clk

Input

System clock derived from the PLL.

avl_clk_wr

Input

Write clock derived from the PLL.

avl_resetn

Input

Reset signal, which you can assert

asynchronously, but you must

deassert synchronously to

avl_clk

.

dll_delay_ctrl[6]

Input

Delay bus for DLL to shift DQS inputs.

DQS mode only.