Opencore plus evaluation, Figure 1–1 – Altera QDRII SRAM Controller MegaCore Function User Manual

Page 7

Altera Corporation

MegaCore Version 9.1

1–3

November 2009

QDRII SRAM Controller MegaCore Function User Guide

About This MegaCore Function

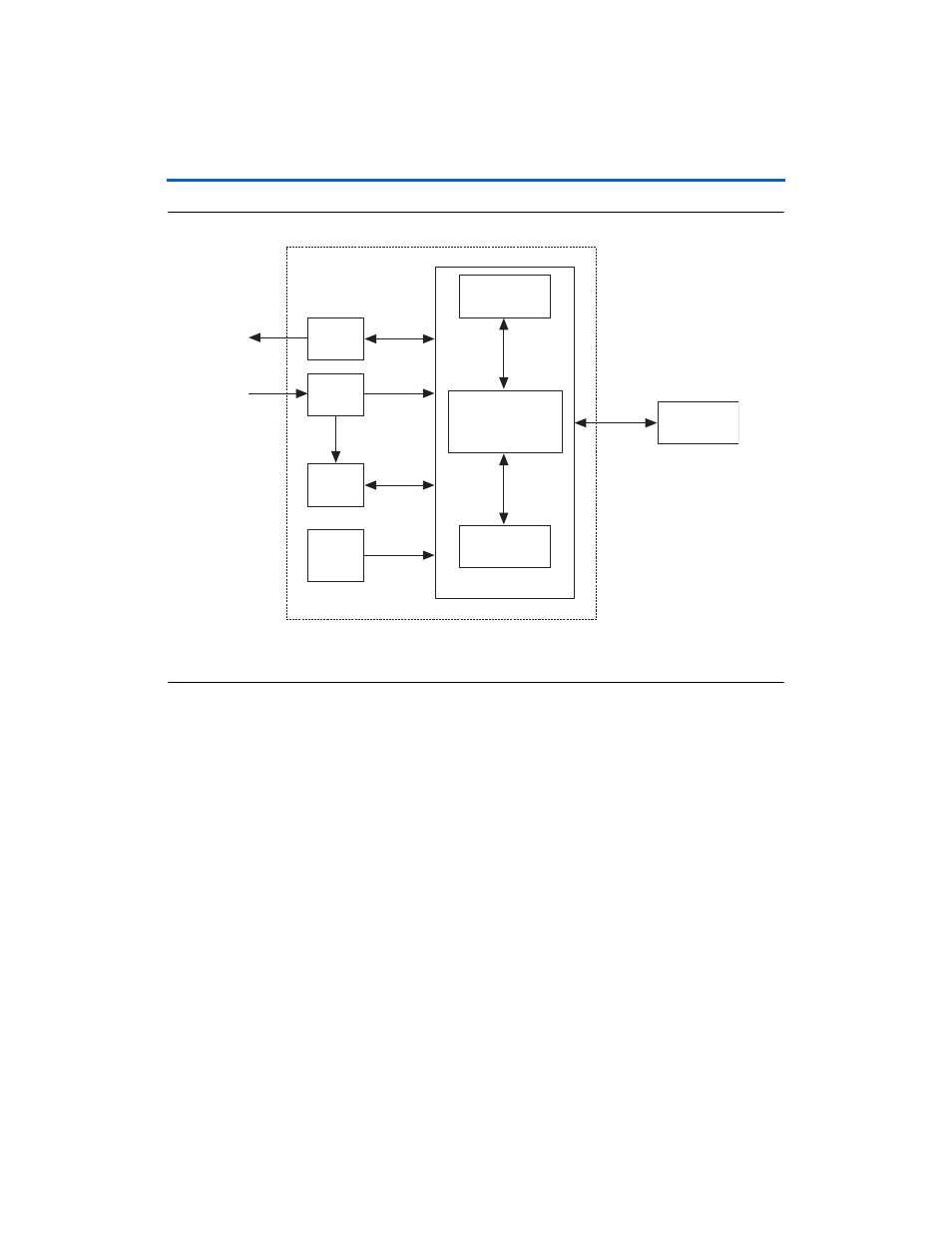

Figure 1–1. QDRII SRAM Controller System-Level Diagram

Notes to

:

(1)

Optional, for Stratix II devices only.

(2)

Non-DQS mode only.

The IP Toolbench-generated example design instantiates a phase-locked

loop (PLL), an optional DLL (for Stratix II devices only), an example

driver, and your QDRII SRAM Controller custom variation. The example

design is a fully-functional example design that can be simulated,

synthesized, and used in hardware. The example driver is a self-test

module that issues read and write commands to the controller and checks

the read data to produce the pass/fail and test complete signals.

You can replace the QDRII SRAM controller encrypted control logic in

the example design with your own custom logic, which allows you to use

the Altera clear-text resynchronization and pipeline logic and datapath

with your own control logic.

OpenCore Plus Evaluation

With Altera’s free OpenCore Plus evaluation feature, you can perform

the following actions:

QDRII SRAM

Example

Driver

System

PLL

Fedback

Clock

PLL (

2)

DLL (

1)

QDRII

SRAM

Interface

Pass

or Fail

Clock

Local

Interface

Example Design

QDRII SRAM Controller

Datapath

(Clear Text)

Control Logic

(Encrypted)

Resynchronization

& Pipeline Logic

(Clear Text)