Altera QDRII SRAM Controller MegaCore Function User Manual

Page 64

3–32

MegaCore Version 9.1

Altera Corporation

QDRII SRAM Controller MegaCore Function User Guide

November 2009

Parameters

shows the read latency options.

shows the capture modes.

shows the pin loading parameters.

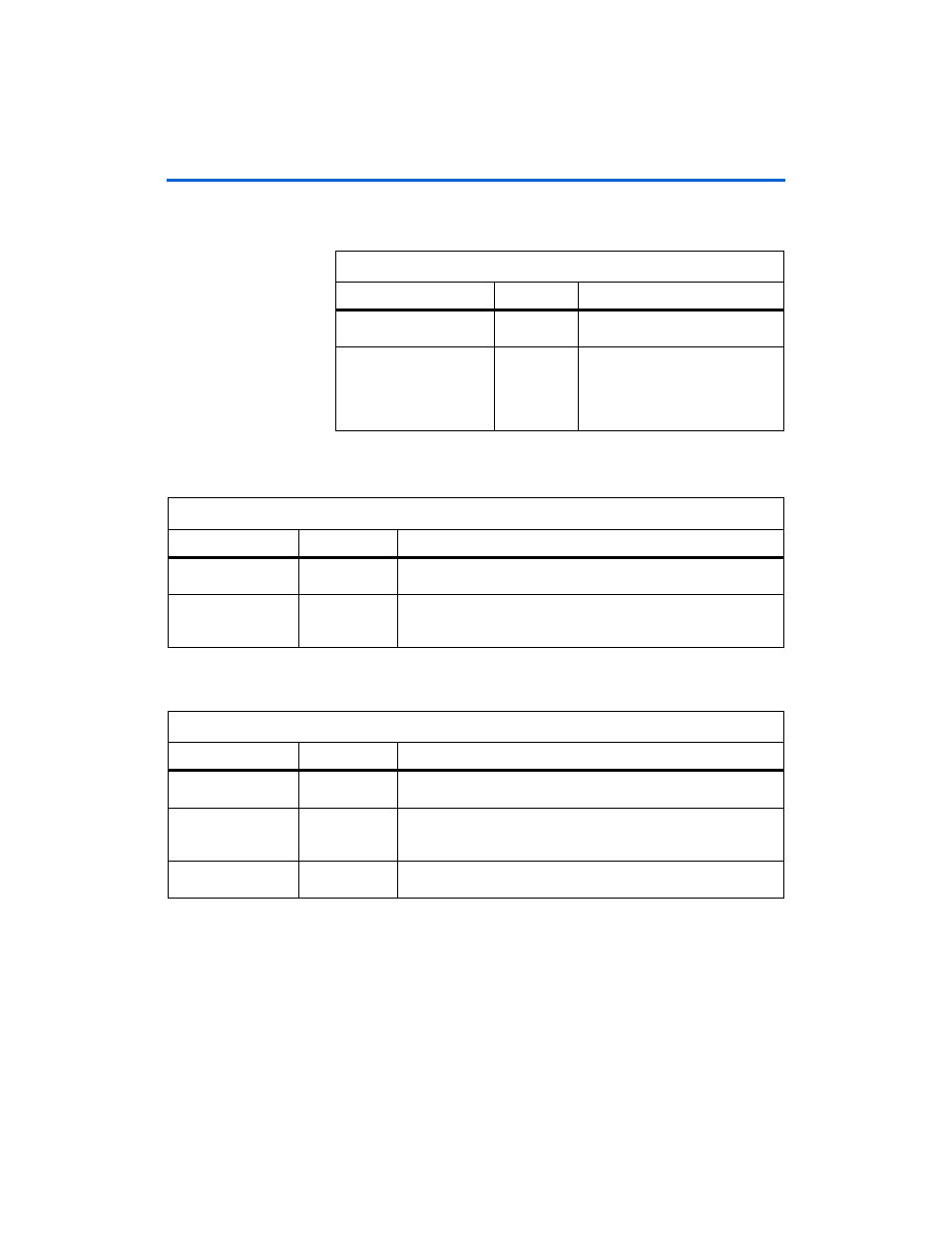

Table 3–12. Read Latency Options

Parameter

Value

Description

Manual read latency

setting

On or off

Turn on if you want to choose the

latency clock cycle.

Set latency to clock cycle

–2 < current

clock cycle <

+4

Choose the latency clock cycle. For

example, if the default is 13, you can

choose any value from 11 to 17.

However, Altera recommends that

you do not alter this parameter.

Table 3–13. Capture Modes

Parameter

Value

Description

DQS mode

On or off

Turn on for DQS capture mode (Stratix II devices only). The controller

is in non-DQS mode only for Stratix devices.

Use migratable byte

groups

On or off

When turned on, you can migrate the design to a migration device

(Stratix II devices only). When turned off the wizard allows much

greater flexibility in the placement of byte groups.

Table 3–14. Pin Loading Parameters

Parameter

Range (pF)

Description

Pin loading on data

pins

Any

Enter the pin loading to match your board and memory devices.

Pin loading on FPGA

address and

command pins

Any

Enter the pin loading to match your board and memory devices.

Pin loading on FPGA

clock pins

Any

Enter the pin loading to match your board and memory devices.