Altera SDI Audio IP Cores User Manual

Page 27

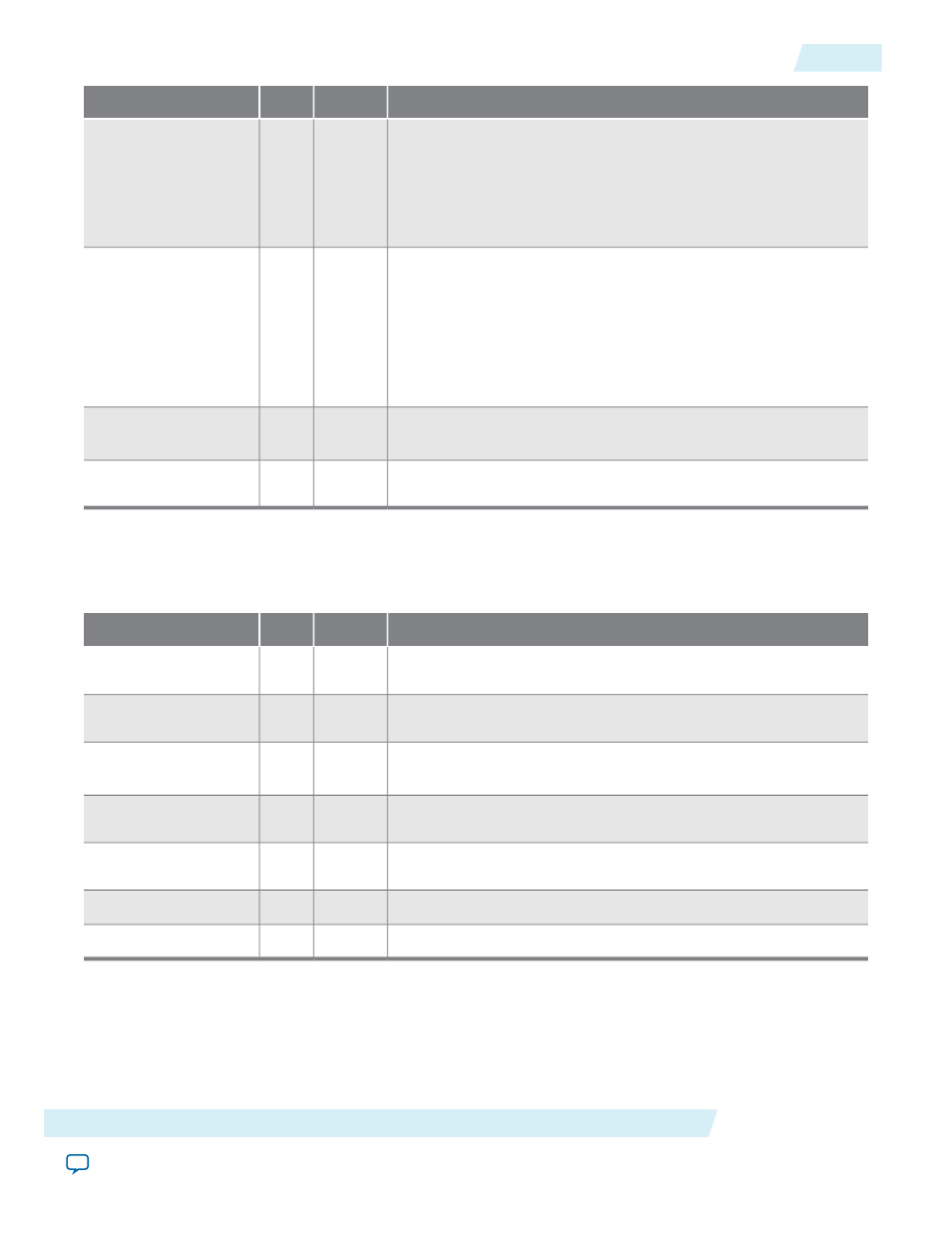

Description

Direction

Width

Signal

Some audio receivers provide a word select output to align the

serial outputs of several audio extract cores. In these circumstances,

assert this signal to control the output timing of the audio extract

externally, otherwise set it to 0. This signal must be a repeating

cycle of high for 32

aud_clk

cycles followed by low for 32

aud_clk

cycles.

Input

[0:0]

aud_ws_in

Assert this data enable signal to indicate valid information on the

aud_ws

and

aud_data

signals.

In synchronous mode, the core ignores this signal.

The core asserts this data enable signal to indicate valid information

on the

aud_ws

and

aud_data

signals.

In synchronous mode, the core drives this signal high.

Output

[0:0]

aud_de

The core asserts this word select signal to provide framing for

deserialization and to indicate left or right sample of channel pair.

Output

[0:0]

aud_ws

The core asserts this signal to extract the internal AES audio signal

from the AES output module.

Output

[0:0]

aud_data

This table lists the Avalon-ST audio signals when you instantiate the SDI Audio Extract IP core in Qsys.

Table 4-10: SDI Audio Extract Avalon-ST Audio Signals

n

is the number of audio channels, the value starts from from 0 to

n

-1.

Description

Direction

Width

Signal

Clocked audio clock. All the audio input signals are synchronous

to this clock.

Input

[0:0]

aud(n)_clk

Avalon-ST ready signal. Assert this signal when the device is able

to receive data.

Output

[0:0]

aud(n)_ready

Avalon-ST valid signal. The core asserts this signal when it receives

data.

Input

[0:0]

aud(n)_valid

Avalon-ST start of packet signal. The core asserts this signal when

it is starting a new frame.

Input

[0:0]

aud(n)_sop

Avalon-ST end of packet signal. The core asserts this signal when

it is ending a frame.

Input

[0:0]

aud(n)_eop

Avalon-ST select signal. Use this signal to select a specific channel.

Input

[7:0]

aud(n)_channel

Avalon-ST data bus. This bus transfers data.

Input

[23:0]

aud(n)_data

This table lists the direct control interface signals. The direct control interface is internal to the SDI Audio

Extract IP core.

Altera Corporation

SDI Audio IP Interface Signals

4-7

SDI Audio Extract Signals

UG-SDI-AUD

2014.06.30