Altdq_dqs2 data ports – Altera ALTDQ_DQS2 User Manual

Page 29

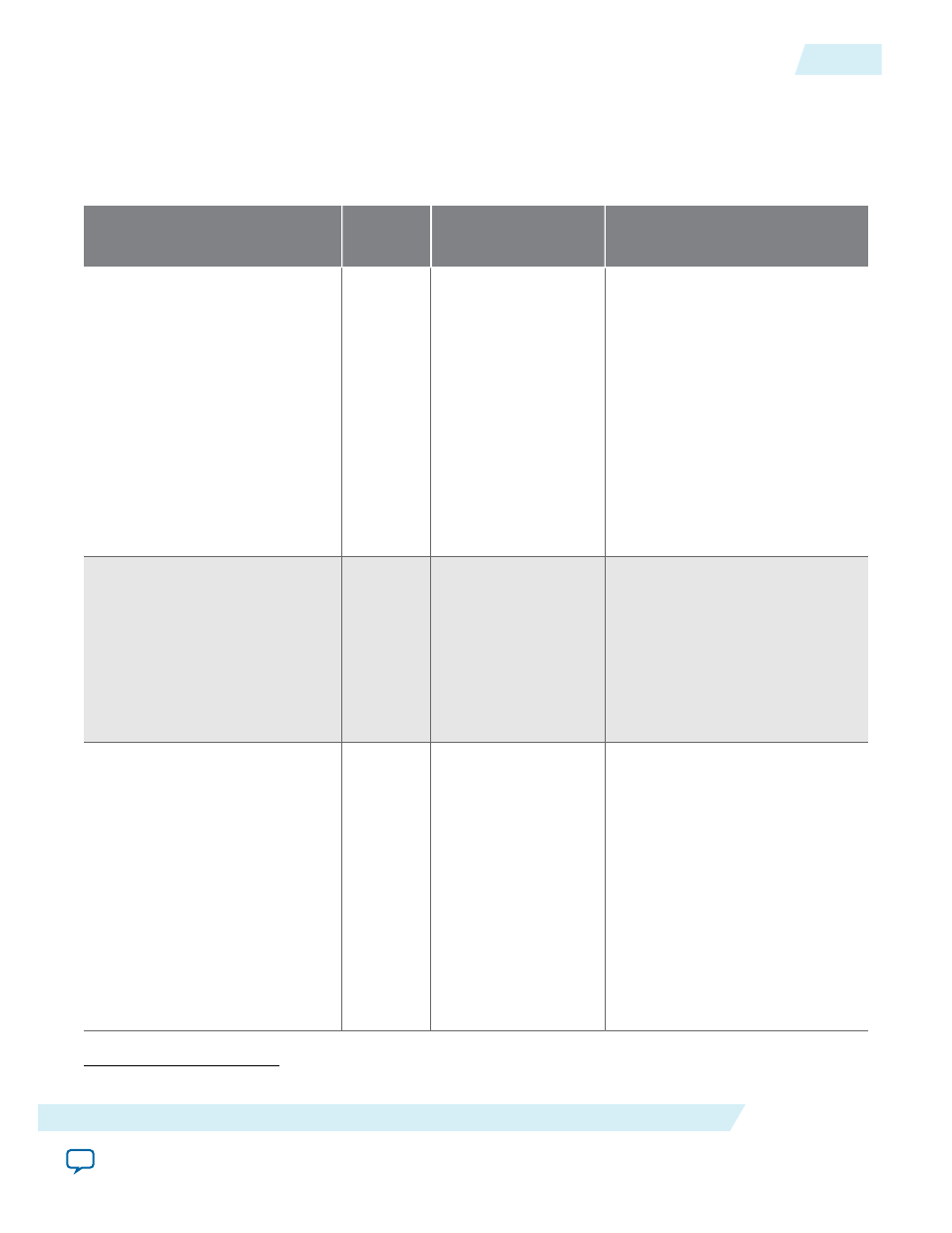

ALTDQ_DQS2 Data Ports

The following table lists the ALTDQ_DQS2 data ports where n= number of DQ pins, m= number of

additional output-only DQ pins, x = 0 to (n-1), and y= 0 to (m-1).

Table 7: ALTDQ_DQS2 Data Ports

Port Name

Type

Width

(2)

Description

extra_write_data_in[]

Input

2m = full-rate

4m = half-rate

Receives data signal from the

core.

This port connects to the input

port of the half-rate data to

single-rate data output registers

block (

mode, only the

extra_write_

data_in[y]

and

extra_write_

data_in[m+y]

ports are used.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

extra_write_data_out[]

Output

m

Sends data to the external device.

This port connects to the output

port of the output buffer (

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

read_data_in[]

Input

n

Receives data from the external

device.

This port connects to the input

port of the input buffer located

between the DQ pin and the

DDR input registers block. This

is an input-only DQ port that

receives data from the external

device (

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

(2)

The port width applies to full-rate mode, unless otherwise specified.

UG-01089

2014.12.17

ALTDQ_DQS2 Data Ports

29

ALTDQ_DQS2 IP Core User Guide

Altera Corporation