Refer to, Dqs configura, Tion block bit sequence – Altera ALTDQ_DQS2 User Manual

Page 42: For arria v gz and, Stratix v devices

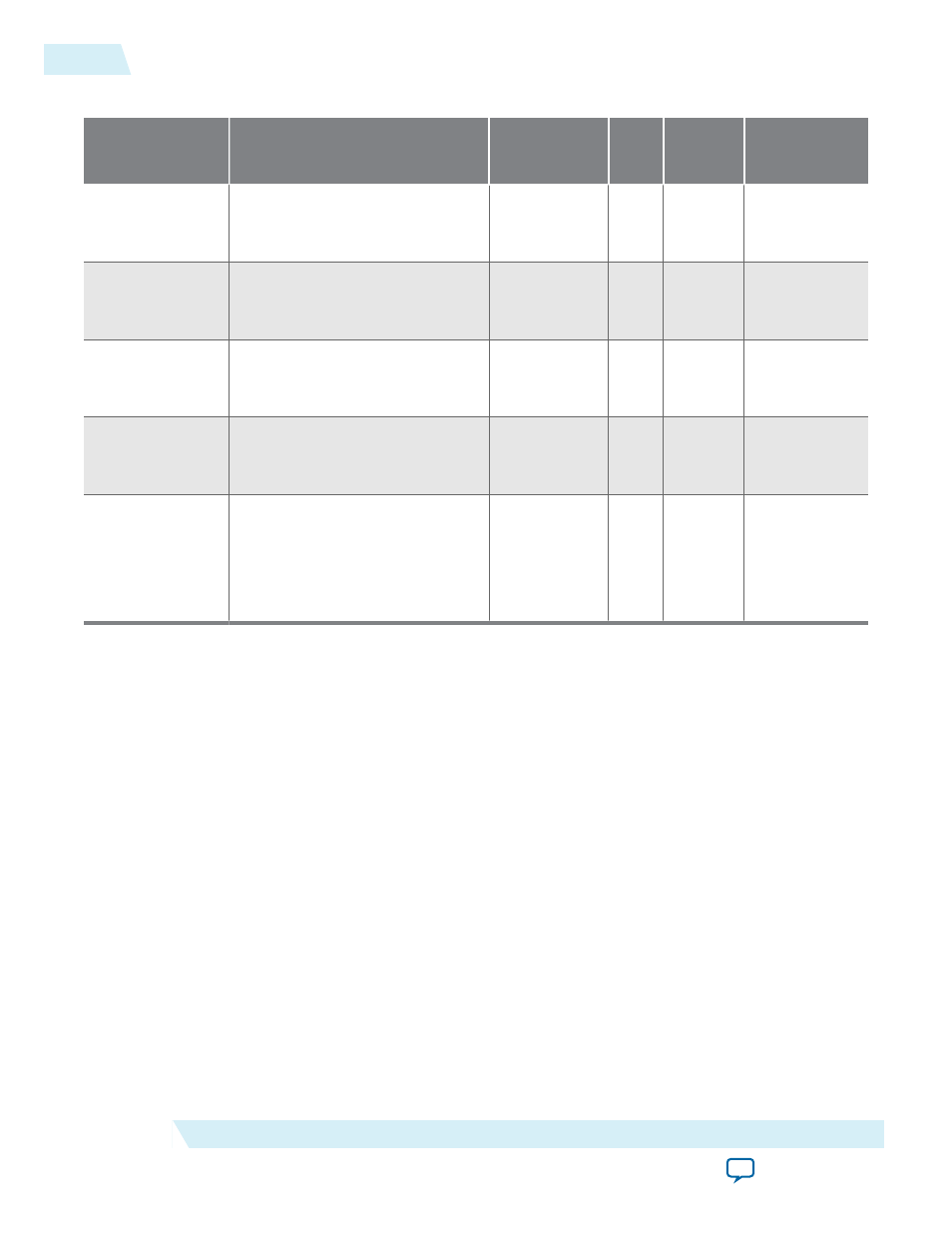

Table 13: I/O Configuration Block Bit Value for Arria V GZ and Stratix V Devices

Bit

Bit Name/

Bit

Default Value

(Binary)

Min.

Value

Max.

Value

Inc. Value

5..0

padtoinputregisterdelaysetting

000000

intrin

sic

delay

787.5 ps +

intrinsic

delay

12.5 ps

11..6

padtoinputregisterrisefalldelayset‐

ting

000000

intrin

sic

delay

787.5 ps +

intrinsic

delay

12.5 ps

17..12

outputdelaysetting1

000000

intrin

sic

delay

787.5 ps +

intrinsic

delay

12.5 ps

23..18

outputdelaysetting2

000000

intrin

sic

delay

787.5 ps +

intrinsic

delay

12.5 ps

39..24

inputclkndelaysetting

inputclkdelaysetting

dutycycledelaymode

dutycycledelaysetting

0000000000000

000

—

—

—

Related Information

DQS Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

The following tables lists the DQS configuration block bit sequence, description, and settings for Arria V

GZ and Stratix V devices.

42

DQS Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide