Altera ALTDQ_DQS2 User Manual

Page 51

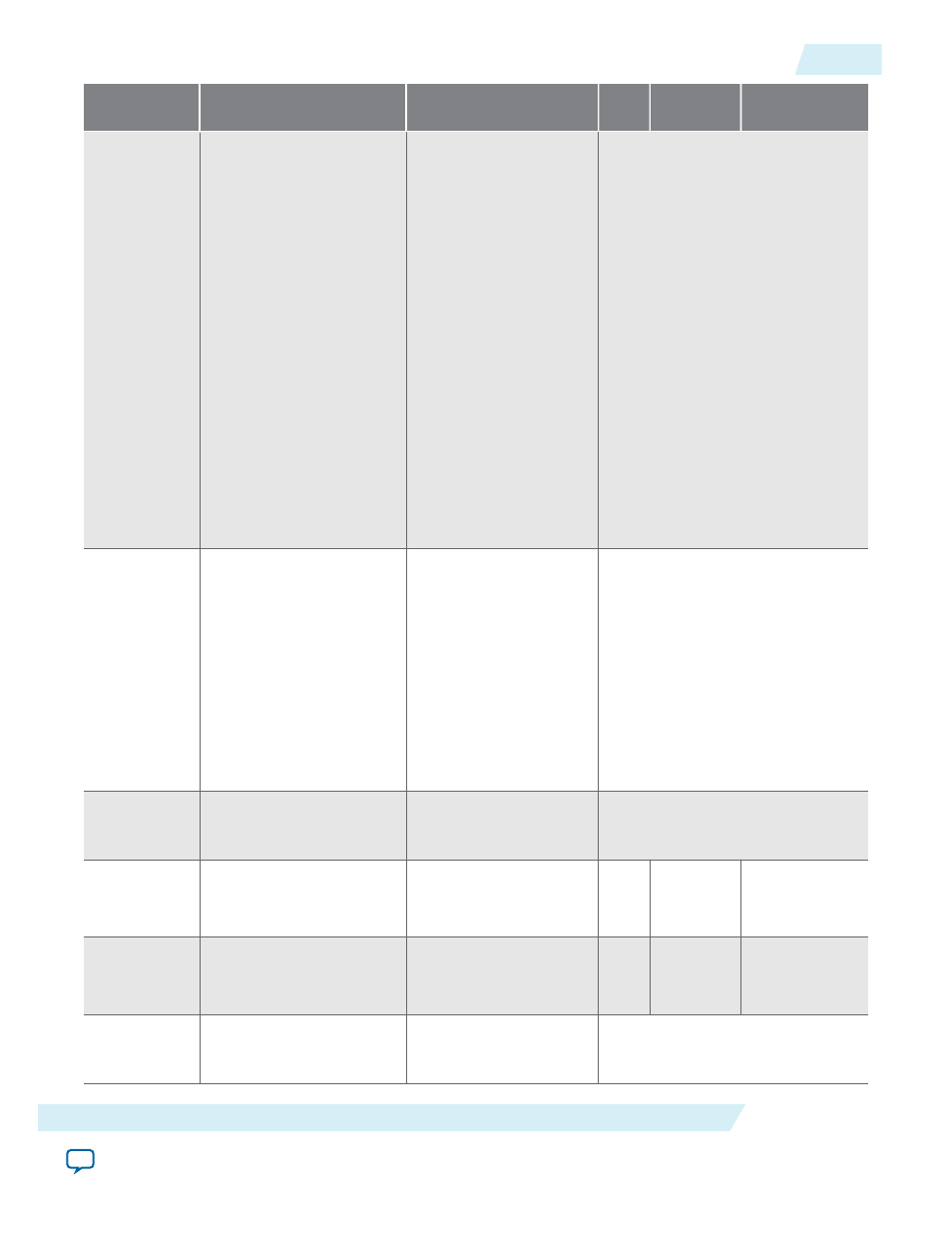

Bit

Bit Name

Default Value (Binary)

Min

Value

Max Value

Inc. Unit

65..46

dqs2xoutputphasesetting

dqs2xoutputpowerdown

dqs2xoutputphaseinvert

dq2xoutputphasesetting

dq2xoutputpowerdown

dq2xoutputphaseinvert

ck2xoutputphasesetting

ck2xoutputpowerdown

ck2xoutputphaseinvert

dqoutputzerophasesetting

postamblezerophasesetting

postamblepowerdown

dividerioehratephaseinvert

dividerphaseinvert

0010_0000_1000_1000_

0100

—

68..66

enaoctcycledelaysetting

10

000: Not supported

001: Not supported

010: No delay

011: 1 cycle delay

100: 2 cycle delay

101: 3 cycle delay

110: Not supported

111: Not supported

69

enaoctphasetransferreg

0

0 = bypass

1 = enable

77..70

dqsdisablendelaysetting

0

intrin

sic

delay

3.2 ns +

intrinsic

delay

12.5 ps

85..78

dqsenabledelaysetting

0

intrin

sic

delay

3.2 ns +

intrinsic

delay

12.5 ps

86

enadqsenablephasetrans‐

ferreg

0

0 = bypass

1 = enable

UG-01089

2014.12.17

DQS Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

51

ALTDQ_DQS2 IP Core User Guide

Altera Corporation